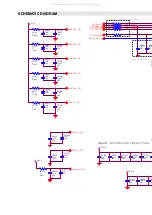

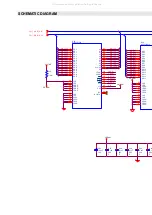

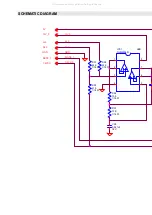

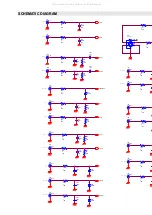

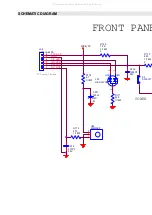

SCHEMATIC DIAGRAM VER1.0

8-13

PIHS

P[11]

T

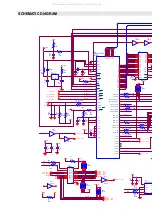

C51

12PF

50V

D

POCLK

R82

4.7

1/16W

D

Y3

14.318MHz

D

DVI_HS

P[10]

D

D

POCLKOSD P[9]

R80

33

1/16W

PLLCLK

P[9]

R81

33

1/16W

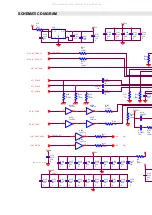

U16

ICS9161A

13

3

6

7

5

1

2

4

8

9

10

11

12

14

15

16

VDD

AVDD

X1

X2

GND

SEL0_CLK

SEL1_DATA

OE

MCLK

VCLK

ERROUT

EXTCLK

INIT0

INIT1

EXTSEL

PD

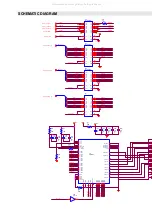

DVI_PICK

P[11]

DATACK

P[8]

RGB-H,V,CLK

C50

0.1uF

25V

Z

FGVS

P[7,8]

T

C52

12PF

50V

V33

L13

0

1/8W

PLLDATA

P[9]

PICLK

P[11]

0

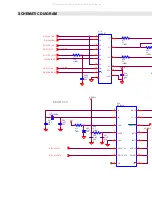

U15

74LVC157

2

3

5

6

11

10

14

13

1

15

4

7

9

12

16

8

1A

1B

2A

2B

3A

3B

4A

4B

A/B

G

1Y

2Y

3Y

4Y

VCC

GND

FGVS

D

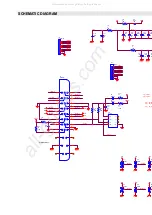

DPWB11393-1G--S

1.0

DIGITAL SYSTEM - HSYN SW & CLOCK GEN.

B

13

16

Tuesday , July 30, 2002

Title

Size

Document Number

Rev

Date:

Sheet

of

Y

DVI-H,V,CLK

RGBn_DVI

P[2,9]

DVI_VS

P[10]

A/B

R79

33

1/16W

C56

0.1uF

25V

Z

1

CLK

PIVS

P[11]

R77

33

1/16W

DDCVSYNC P[8]

D

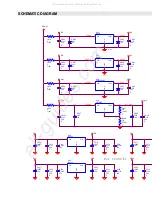

VCCPLL

PIHSS

P[8]

R78

33

1/16W

R83

33

1/16W

+

C55

47uF

16V

POCLK

P[11,14]

FGHS

P[7,8]

TP28

VCCPLL

D

PLLHSO

P[8]

C57

0.1uF

25V

Z

FGHS

FROM CPU

V33SB

R386

150

1/16W

CLK

P[11,12]

T

C404

22PF

50V

D

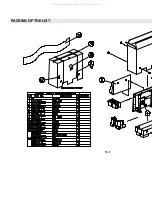

All manuals and user guides at all-guides.com