16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

+

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

_

BOTTOM

PEAK

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

3 STATE

DET.

SW3

SW2

SW1

H

H

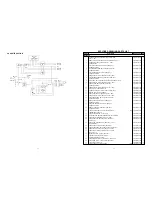

AGC Amp.

1

0

p

F

60K

Ω

FEO

FEN

SSB

VRO

20K

Ω

11K

Ω

11K

Ω

2

0

K

Ω

100K

Ω

1

0

0

K

Ω

1

0

0

K

Ω

20K

Ω

20K

Ω

20K

Ω

12K

Ω

10K

Ω

10K

Ω

30K

Ω

20K

Ω

10K

Ω

3

0

K

Ω

48K

Ω

2.9K

Ω

238K

Ω

238K

Ω

150K

Ω

20K

Ω

60K

Ω

60K

Ω

90K

Ω

1

5

0

K

Ω

1K

Ω

1K

Ω

83K

Ω

1K

Ω

1.4K

Ω

2.26K

Ω

2

1

.8

2

K

Ω

15K

Ω

15K

Ω

50K

Ω

12K

Ω

RFRP

BTC

RFCT

PKC

RFRPIN

RFGO

GVSW

AGCIN

RFO

GND

RFN2

36pF

3pF

10pF

3

p

F

15pF

15pF

40pF

4

0

p

F

SBAD

TEO

TEN

2VRO

TEB

SEL

LDO

MDI

TNI

TPI

FPI

FNI

GMAD

RFGC

V

CC

IC2 TA2153FN

S

E

L

SERVO

control

ROW

RAW

Digital equailzer

Automatic adjustment

Circuit

Clock gene.

CLV

servo

Sub code decoder

Synchronous

Guarantee EFM

decode

VCO

PWM

DA

AD

CD clock

X

't

a

l O

S

C

1

b

it

D

A

C

16K SRAM

Correction circuit

Audio out

Digital out

Micon interface

X'tal OSC

MPX

Port1

Timer

Port4

Port3

BUZR

AD

Canv.

interrupt

Cont

Serial

interface

Data Reg(16 bit)

ROM

(16x12288 Step)

Program

Counter

Stack Reg.

(8 Level)

Bias

A

d

d

re

s

s

OT 19-22

G-Reg.

R/W Buf.

ALU

RAM

(4x512 word)

instruction

Decoder

LCD Driver/Output Port

Port8

P

o

rt

2

F/F

Power On Reset

ZDET,CLCK,DATA,SFSY,LRCK,BCK,MBOV,IPF

Data

slicer

+

+

+

VREF

VREF

R

E

F

R

E

F

2

V

D

M

O

F

M

O

T

E

B

C

R

F

G

C

V

T

R

O

F

O

O

T

E

Z

I

T

E

I

S

B

A

D

F

E

I

R

F

P

R

R

F

Z

I

R

F

C

I

A

V

A

V

D

D

S

S

VREF

RFI

SLCO

TMAX

PDD

P2VREF

VCOF

PVREF

LPFO

+

LPFN

SBOK

SBSY

DOUT

OT22(COFS)

OT21(SPDA)

OT20(SPCK)

OT19(HSO)

HOLD

TESTM

TESTC

IN1

IN2

P2-0

P2-1

P2-2

P2-3

RST

MVDD

MVSS

P

8

-3

(S

1

8

/I

P

F

)

P

8

-2

(S

1

7

/M

B

O

V

)

P

8

-1

(S

1

8

/A

O

U

T

)

P

8

-0

(S

1

5

/B

C

K

)

S

1

0

(O

T

1

4

/Z

D

E

T

)

S

1

1

(O

T

1

5

/C

L

C

K

)

S

1

2

(O

T

1

6

/D

A

T

A

)

S

1

3

(O

T

1

7

/S

F

S

Y

)

S

1

4

(O

T

1

8

/L

R

C

K

)

C

O

M

1

(O

T

1

)

C

O

M

2

(O

T

2

)

C

O

M

3

(O

T

3

)

C

O

M

4

(O

T

4

)

S

1

(O

T

5

)

S

2

(O

T

6

)

P3-3(Adin3)

P3-2(Adin2)

P3-1(Adin1)

P3-0

P4-0(Adin4

/BUZR)

P4-1(SI2)

P4-2(S10/

S11/SDA)

P4-3(SCK

/SCL)

INTR

SBSY

MXO

MXI

P1-3(K3)

P1-0(K0)

VDD

VSS

L

P

F

DVSR

RO

DVRR

DV DD

DVRL

LO

DVSL

XVSS

XI

XO

XVDD

ZDET

CD Reset

R

e

s

e

t

CLCK,DATA,SFSY,

LRCK,BCK,MBOV,IPF

SBSY

CPU clock

IC1 TC94A09F-202

38

37

L-ch

R-ch

LATCH

LATCH

DATA DECODER,STB GENERATOR

SHIFT REGISTER(13bit)

15

14

13

12

11

10

9

2

3

4

5

6

7

8

1

16

OUT

IN

LD1

LD2

A-GND

CS

CK

OUT

IN

LD1

LD2

A-GND

STB

DATA

VSS

VDD

L-ch

VOLUME

R-ch

VOLUME

IC502 TC9260P

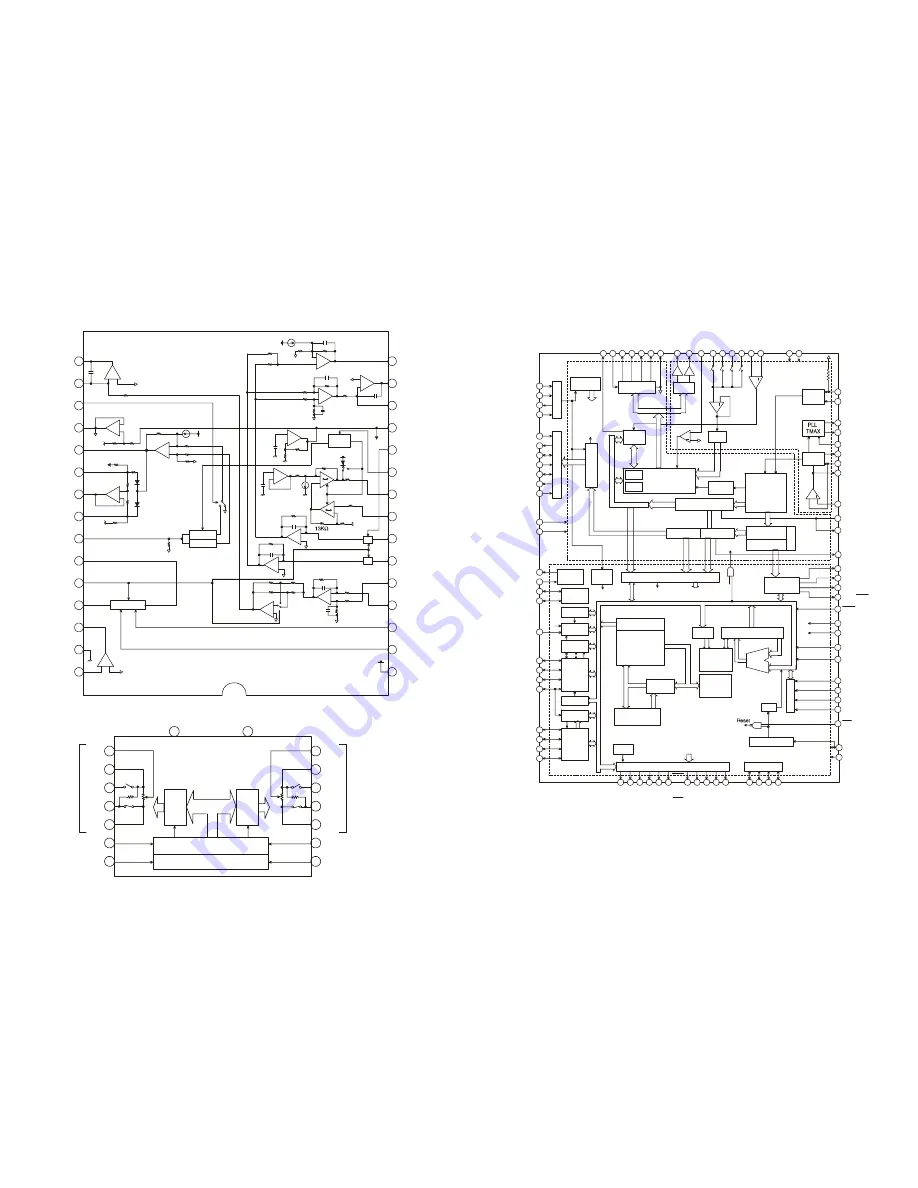

Содержание QX-D3305

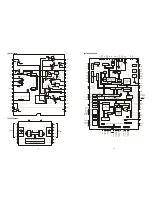

Страница 9: ...16 15 CASSETTE CD PCB CD6606 01 02 ...

Страница 10: ...POWER PCB CD6606 01 03 b b b b b 18 17 ...

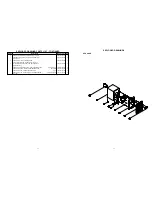

Страница 11: ...20 19 KEY DISPLAY PCB CD6606 01 08 RECTIFIER PCB CD6606 01 09 ...

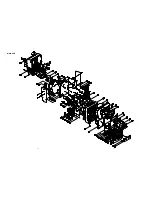

Страница 25: ...48 47 MAIN UNIT ...

Страница 26: ...NOTES Printed in China March 2004 808 66085W 010 ...