34

Chapter 2

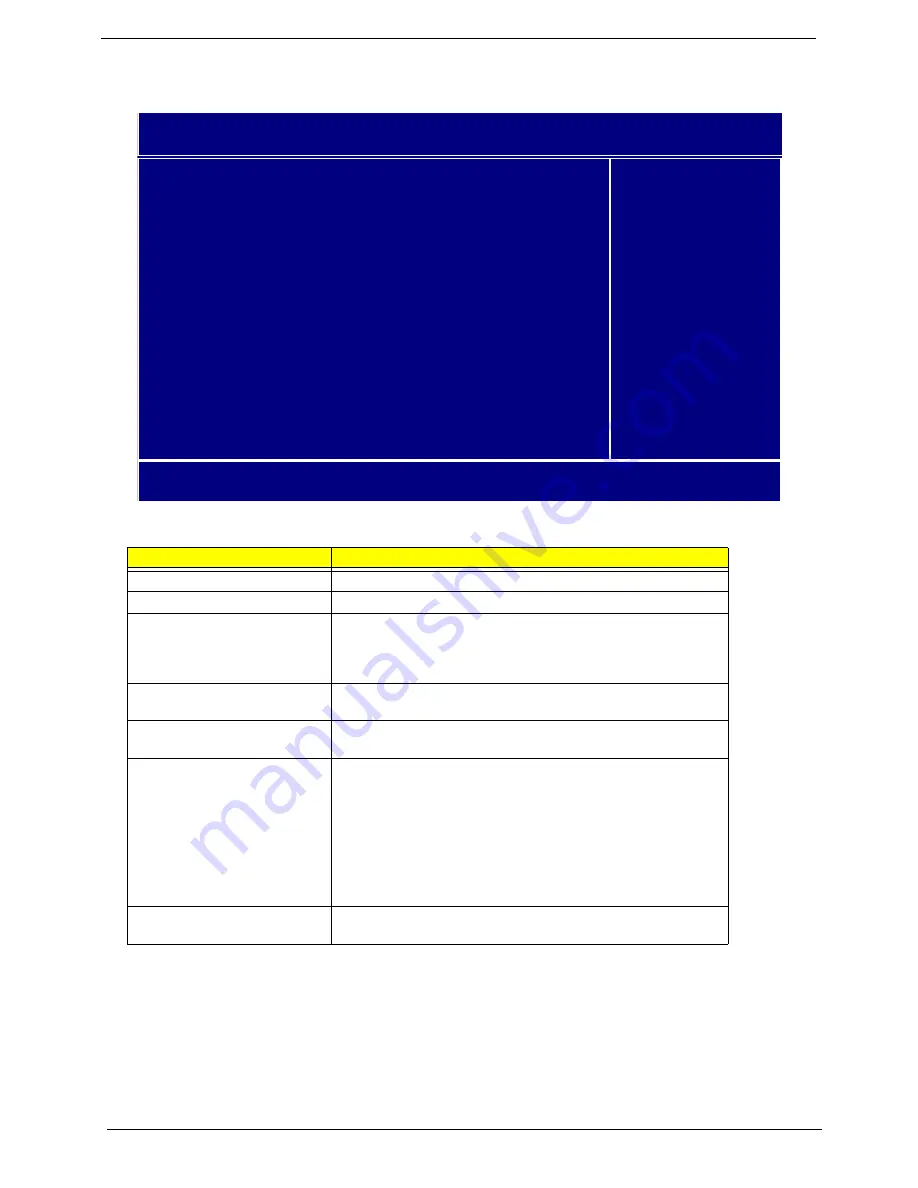

DRAM Clock/Timing Control

Parameter

Description

Current CPU Frequency

Detect the current CPU Frequency

Current DRAM Frequency

Detect the current DRAM Frequency

DRAM Timing Control

Enables you to select the CAS latency time in HCLKs of 2, 2.5, or 3.

The value is set at the factory depending on the DRAM installed. Do

not change the values in this field unless you change specifications of

the installed DRAM or the installed CPU.

DRAM CAS Latency

This item controls the timing delay (in clock cycles) before the DRAM

starts a read command after receiving it.

RAS Active Time (tRAS)

This item allows you to set the amount of time a RAS can be kept

open for multiple accesses. High figures will improve performance.

RAS Precharge Time (tRP)

This is the duration of the time interval during which the Row Address

Strobe signal to a DRAM is held low during normal Read and Write

Cycles. This is the munimum interval between completing one read

or write and starting another from the same (non-page mode) DRAM.

Techniques such as memory interleaving, or use of Page Mode

DRAM are often used to avoid this delay. Some chipsets require this

parameter in order to set up the memory configuration properly. The

RAS Precharge value is typically about the same as the RAM Access

(data read/write) time.

RAS to CAS Delay (tRCD)

This is the amount of time a CAS is performed after a RAS. This

lower the better, but some DRAM does not support low figures.

Current CPU Frequency

133 MHz

Item Help

Current DRAM Frequency 200 MHz

DRAM Timing Control

[By SPD]

Menu Level

X

x DRAM CAS Latency

2.5T

x RAS Active Time (tRAS)

6T

x RAS Recharge Time (tRP) 3T

x RAS to CAS Delay (tRCD) 3T

Phoenix - AwardBIOS CMOS Setup Utilitye

DRAM Clock/Timing Control

KLIJ

: Move Enter: Select +/-/PU/PD: Value F10:Save ESC: Exit F1: General Help

F5: Previous Values F7: Optimized Defaults

Содержание Aspire SA85

Страница 80: ...74 Chapter 6 Exploded Diagram ...