12. Timer 0/1/2/3/4/5

A96G140/A96G148/A96A148 User’s manual

126

X

1

2

4

5

6

8

M-1

0

1

3

4

Timer 3 clock

Counter

T3ADRH/L

T3 Interrupt

PWM3O

B Match

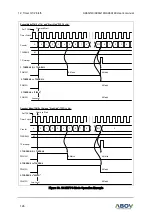

Repeat Mode(T3MS = 11b) and "Start High"(T3POL = 0b).

Set T3EN

0

Clear and Start

3

7

2

M

A Match

1. T3BDRH/L(5) < T3ADRH/L

PWM3O

A Match

2. T3BDRH/L >= T3ADRH/L

PWM3O

A Match

3. T3BDRH/L = "0000H"

Low Level

X

1

2

4

5

6

8

M-1

0

Timer 3 clock

Counter

T3ADRH/L

T3 Interrupt

PWM3O

B Match

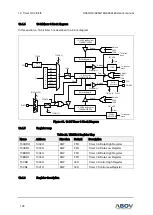

One-shot Mode(T3MS = 10b) and "Start High"(T3POL = 0b).

Set T3EN

0

Clear and Start

3

7

M

A Match

1. T3BDRH/L(5) < T3ADRH/L

PWM3O

A Match

2. T3BDRH/L >= T3ADRH/L

PWM3O

A Match

3. T3BDRH/L = "0000H"

Low Level

Figure 60. 16-bit PPG Mode Operation Example