72

RX-V1

065/HTR-6280/

AX-V1

065

RX-V1065/HTR-6280/AX-V1065

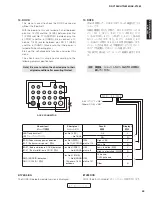

No.

Function Name

(P.C.B.)

TYPE

(1)

PULL

(2)

GPIO

(3)

Detail of Function

62

VSS

63

EM_D[10]

IO

–

N

EMIF data bus [lower 16-Bits]

64

EM_D[9]

IO

–

N

EMIF data bus [lower 16-Bits]

65

CVDD

66

EM_D[8]

IO

–

N

EMIF data bus [lower 16-bits]

67

EM_WE_DQM[1]

O

–

N

Write enable or byte enable for EM_D [15:8]

68

DVDD

69

VSS

70

EM_CLK

O

–

N

SDRAM clock

71

EM_CKE

O

–

N

SDRAM clock enable

72

VSS

73

DVDD

74

EM_A[11]

O

–

N

EMIF address bus

75

EM_A[9]

O

–

N

EMIF address bus

76

EM_A[8]

O

–

N

EMIF address bus

77

CVDD

78

VSS

79

EM_A[7]

O

–

N

EMIF address bus

80

EM_A[6]

O

–

N

EMIF address bus

81

DVDD

82

VSS

83

EM_A[5]

O

–

N

EMIF address bus

84

EM_A[4]

O

–

N

EMIF address bus

85

CVDD

86

EM_A[3]

O

–

N

EMIF address bus

87

VSS

88

EM_A[2]

O

–

N

EMIF address bus

89

EM_A[1]

O

–

N

EMIF address bus

90

CVDD

91

EM_A[0]

O

–

N

EMIF address bus

92

DVDD

93

EM_A[10]

O

–

N

EMIF address bus

94

EM_BA[1]

O

–

N

SDRAM bank address and asynchronous memory Low-Order address

95

VSS

96

EM_BA[0]

O

–

N

SDRAM bank address and asynchronous memory Low-Order address

97

EM_CS[0]

O

–

N

SDRAM chip select

98

EM_RAS

O

–

N

SDRAM row address strobe

99

VSS

100

EM_CS[2]

O

–

N

Asynchronous memory chip Select

101

CVDD

102

NC

O

–

N

Asynchronous memory read/not write

103

DVDD

104

EM_OE

O

–

N

SDRAM output enable

105

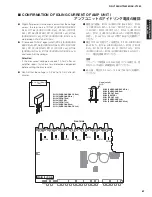

SPI0_ENA/I2C1_SDA

IO

–

Y

SPI0 enable (ready) or I2c1 serial data

106

VSS

107

SPI0_ENA/I2C1_SCL

IO

–

Y

SPI0 enable (ready) or I2c1 serial clock

108

SPI0_CLK/I2C0_SCL

IO

–

Y

SPI0 serial clock or I2c0 serial clock

109

VSS

110

SPIO_SIMO

IO

–

Y

SPI0 data pin slave in master out

111

SPIO_SOMI/I2C0_SDA

IO

–

Y

SPI0 data pin slave out master in or I2C0 serial data

112

DVDD

113

AXR0[0]

IO

–

Y

McASP0 serial data 0

114

VSS

115

AXR0[1]

IO

–

Y

McASP0 serial data 1

116

AXR0[2]

IO

–

Y

McASP0 serial data 2

117

AXR0[3]

IO

–

Y

McASP0 serial data 3

118

VSS

119

AXR0[4]

IO

–

Y

McASP0 serial data 4

120

SPI1_SCS

IO

–

Y

McASP0 serial data 5 or SPI1 slave chip select

121

SPI1_ENA

IO

–

Y

McASP0 serial data 6 or SPI1 enable (ready)

122

SPI1_CLK

IO

–

Y

McASP0 serial data 7 or SPI1 serial clock

Summary of Contents for RXV1065 - RX AV Receiver

Page 5: ...5 RX V1065 HTR 6280 AX V1065 RX V1065 HTR 6280 AX V1065 AX V1065 J model...

Page 9: ...9 RX V1065 HTR 6280 AX V1065 RX V1065 HTR 6280 AX V1065 HTR 6280 C model AX V1065 J model...

Page 162: ...RX V1065 HTR 6280 AX V1065 162...

Page 163: ...163 RX V1065 HTR 6280 AX V1065 RX V1065 HTR 6280 AX V1065...

Page 164: ...164 RX V1065 HTR 6280 AX V1065 RX V1065 HTR 6280 AX V1065...

Page 165: ...165 RX V1065 HTR 6280 AX V1065 RX V1065 HTR 6280 AX V1065 MEMO...

Page 166: ...RX V1065 HTR 6280 AX V1065...