Virtex-5 FPGA User Guide

295

UG190 (v5.0) June 19, 2009

Specific Guidelines for I/O Supported Standards

Transmitter Termination

The Virtex-5 FPGA LVDS transmitter does not require any external termination.

lists the allowed attributes corresponding to the Virtex-5 FPGA LVDS current-mode

drivers. Virtex-5 FPGA LVDS current-mode drivers are a true current source and produce

the proper (EIA/TIA compliant) LVDS signal.

Receiver Termination

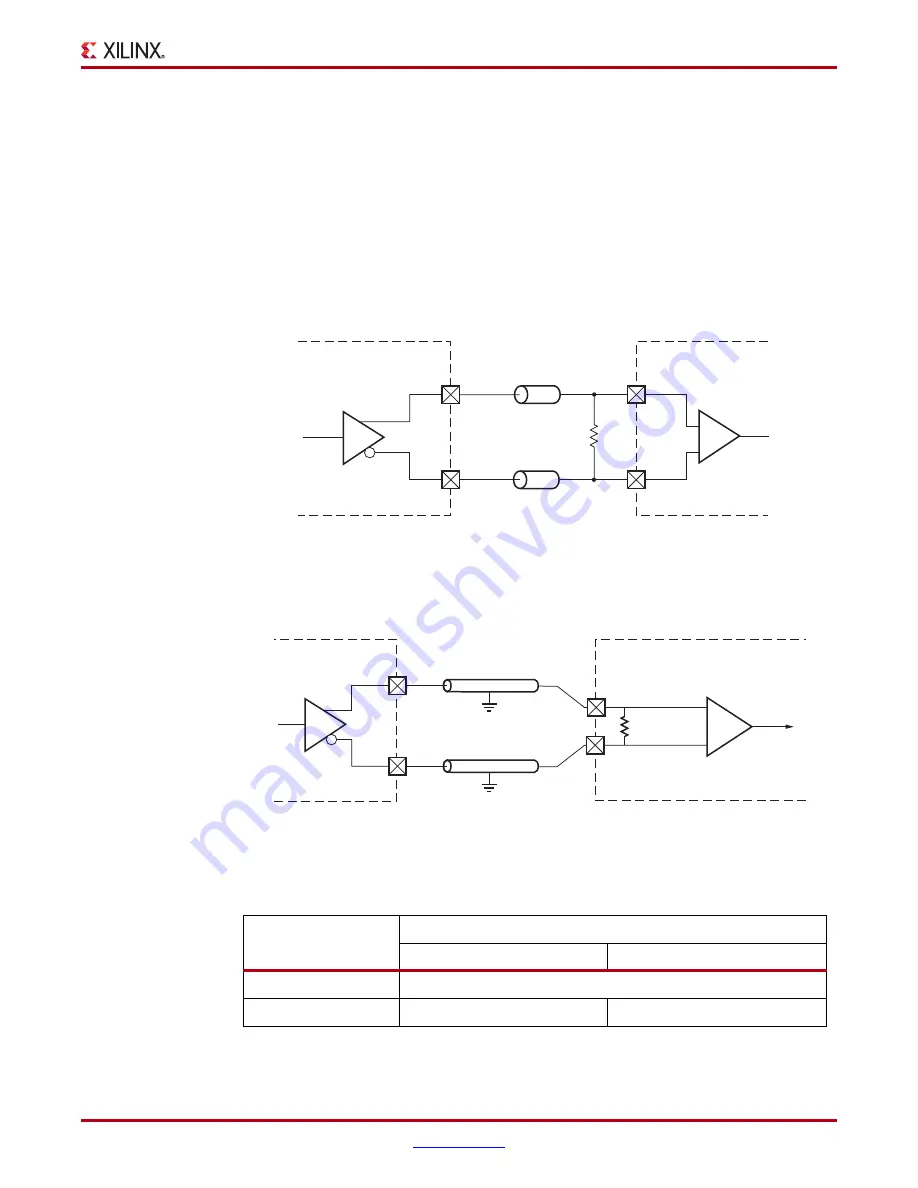

is an example of differential termination for an LVDS receiver on a board with

50

Ω

transmission lines.

is an example of a differential termination for an LVDS receiver on a board with

50

Ω

transmission lines.

lists the available Virtex-5 FPGA LVDS I/O standards and attributes supported.

X-Ref Target - Figure 6-87

Figure 6-87:

LVDS_25 Receiver Termination

X-Ref Target - Figure 6-88

Figure 6-88:

LVDS_25 With DIFF_TERM Receiver Termination

Table 6-36:

Allowed Attributes of the LVDS I/O Standard

Attributes

Primitives

IBUFDS/IBUFGDS

OBUFDS/OBUFTDS

IOSTANDARD

LVDS_25, LVDSEXT_25

DIFF_TERM

TRUE, FALSE

N/A

ug190_6_81_030506

+

–

External Termination

Z0

IOB

IOB

LVDS_25

LVDS_25

Z0

RDIFF = 2Z0= 100

Ω

ug190_6_82_030506

Data in

Z

0

= 50

Ω

Z

0

= 50

Ω

RDIFF= 100

Ω

LVDS_25

LVDS_25

+

–

0

0

IOB

IOB

Summary of Contents for Virtex-5 FPGA ML561

Page 1: ...Virtex 5 FPGA User Guide UG190 v5 0 June 19 2009 ...

Page 8: ...Virtex 5 FPGA User Guide www xilinx com UG190 v5 0 June 19 2009 ...

Page 20: ...20 www xilinx com Virtex 5 FPGA User Guide UG190 v5 0 June 19 2009 ...

Page 24: ...24 www xilinx com Virtex 5 FPGA User Guide UG190 v5 0 June 19 2009 Preface About This Guide ...

Page 172: ...172 www xilinx com Virtex 5 FPGA User Guide UG190 v5 0 June 19 2009 Chapter 4 Block RAM ...