HH

VS1005 VSOS A

UDIO

S

UBSYSTEM

VS1005g

FMR

FML

Mono

Right

Left

AD_CF_DEC6SEL

AD_CF_DEC6ENA

ANA_CF3

_GAIN2

ANA_CF0

ANA_CF0

ANA_CF3

_GAIN1

ANA_CF0

ANA_CF0

I

Q

BLUE: Register or register bit(s)

RED: Pin

Digital

Analog and RF

18

18

AD_LEFT

DEC6_LEFT

DEC6_RIGHT

DIA1

LINE1_1

LINE2_1

LINE3_1

RF_N

RF_P

LINE1_2

LINE2_2

LINE3_2

LINE1_3

L

R

6

18

18

SP_LDATA

SP_RDATA

24

24

SPDIF_IN

24

AD_CF_ADFS

ADENA

AD_CF_

AD1

S/PDIF

decoder

demod.

FM

DIA2

DIA3

VCO

AD_RIGHT

AD_MONO

24

24

24

24

24

AD_CF_ADFS

FM_CF_UAD3

AD_CF_

AD3ENA

AD3

AD_CF_

ADENA

AD2

MIC2N

MIC2P

MIC1P

MIC1N

FM_CF_UAD1

FM_CF_UAD2

AD23_FLP

AD_CF_

AD_CF_AD3FS

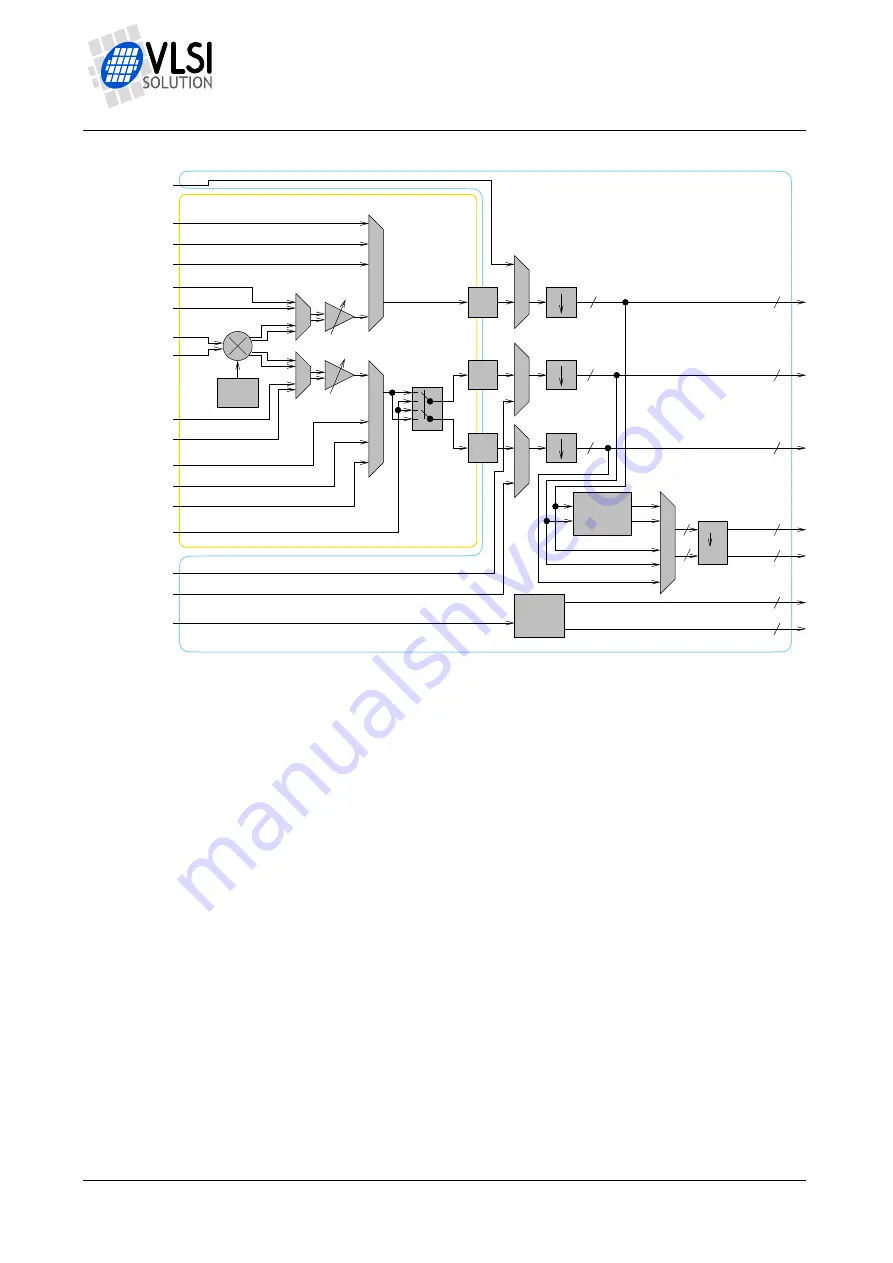

Figure 2: VS1005g recording (AD, FM, etc) signal paths

Figure 2 shows the VS1005 hardware input audio paths. Many of these have a driver

controlling them.

Rev. 3.57

2019-04-10

Page