17

(UMC5N) and Q1018 to disable the supply voltage

to the Power Module Q1019, thus disabling the trans-

mitter.

Spurious Suppression

Generation of spurious products by the transmitter

is minimized by the fundamental carrier frequency

being equal to final transmitting frequency, modu-

lated directly in the transmit VCO. Additional har-

monic suppression is provided by a low-pass filter

consisting of L1004, L1005, and, L1006 and C1013,

C1014, C1015, C1017, C1019, and C1020, resulting

in more than 60 dB of harmonic suppression prior

to delivery of the RF signal to the antenna.

PLL Frequency Synthesizer

The PLL frequency synthesizer consists of the VCO

(Q1033

2SK508-K52

: RX and Q1039

2SC4227

: TX),

VCO buffers Q1034 (

2SC5226-4/5

), Q1041

(

2SC5226-4/5

), Q1030 (

2SC5226-4/5

), PLL sub-

system IC Q1054 (

SA7025DK

) and 14.6MHz refer-

ence crystal X1002.

The frequency stability is ±2.5 ppm within the tem-

perature range of –22°F to +140°F (–30°C to +60°C).

The output of the 14.6 MHz reference is applied to

pin 8 of the PLL IC. While receiving, VCO Q1033

oscillates between 355.75 and 467.75 MHz accord-

ing to the transceiver version and the programmed

receiving frequency. The VCO generates this 355.75

to 467.75 MHz frequency for provision of the first

local signal. While transmitting, the VCO generates

a signal at 400 to 512 MHz.

The output of the VCO is amplified by Q1041 and

routed to the pin 5 of the PLL IC. The output of the

VCO is also amplified by Q1030 and routed to the

first local or Power Module according to D1031.

The PLL IC consists of a prescaler, fractional divider,

reference divider, phase comparator, and charge

pump. This PLL IC is a fractional-N type synthesizer

and operates using a 40, 50, or 60 kHz reference sig-

nal which is the eighth harmonic of the channel step

(5, 6.25 or 7.5 kHz). The input signal from pins 5 and

8 of the PLL IC is divided down to 40/50/60 kHz and

compared at the phase comparator. The pulsed out-

put signal of the phase comparator is applied to the

charge pump and transformed into a DC signal in

the loop filter. The DC signal is applied to the pin 1

of the VCO and locked to keep the VCO frequency

constant.

PLL data is put out from “DTA” (pin 100), “CLK”

(pin 2) and “PSTB” (pin 98) of the microprocessor

Q1048. The data are passed to the PLL IC when the

channel is changed or when transmission is switched

to reception (and vice versa). The “PLL lock” condi-

tion is always monitored by pin 20 of Q1048. When

the PLL is unlocked, the “UL” line goes low.

Miscellaneous Circuits

Push-To-Talk Transmit Activation

The PTT switch on the microphone is connected to

pin 36 of microprocessor Q1048, so that when the

PTT switch is closed, pin 85 of Q1048 goes high. This

signals the microprocessor to activate the TX/RX con-

troller Q1004 (

UMG2N

), which then disables the re-

ceiver by disabling the 5V supply bus at Q1011

(

UN911F

) to the front-end, FM IF subsystem IC

Q1046, and receiver VCO circuitry.

At the same time, Q1003 (

XP1501

) and Q1002

(

CPH6102

) activate the TX 5V supply line to enable

the transmitter.

Circuit Description

Summary of Contents for VX-800

Page 10: ...10 Set Menu Mode Functions Note ...

Page 13: ...13 Block Diagram ...

Page 14: ...14 Note Block Diagram ...

Page 24: ...24 Note ...

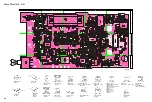

Page 26: ...26 Main Unit Lot 1 3 Note ...

Page 29: ...29 Main Unit Lot 4 50 Circuit Diagram ...

Page 30: ...30 Main Unit Lot 4 50 Note ...

Page 33: ...33 Main Unit Lot 51 Circuit Diagram ...

Page 34: ...34 Main Unit Lot 51 Note ...