ZED-F9K - Integration manual

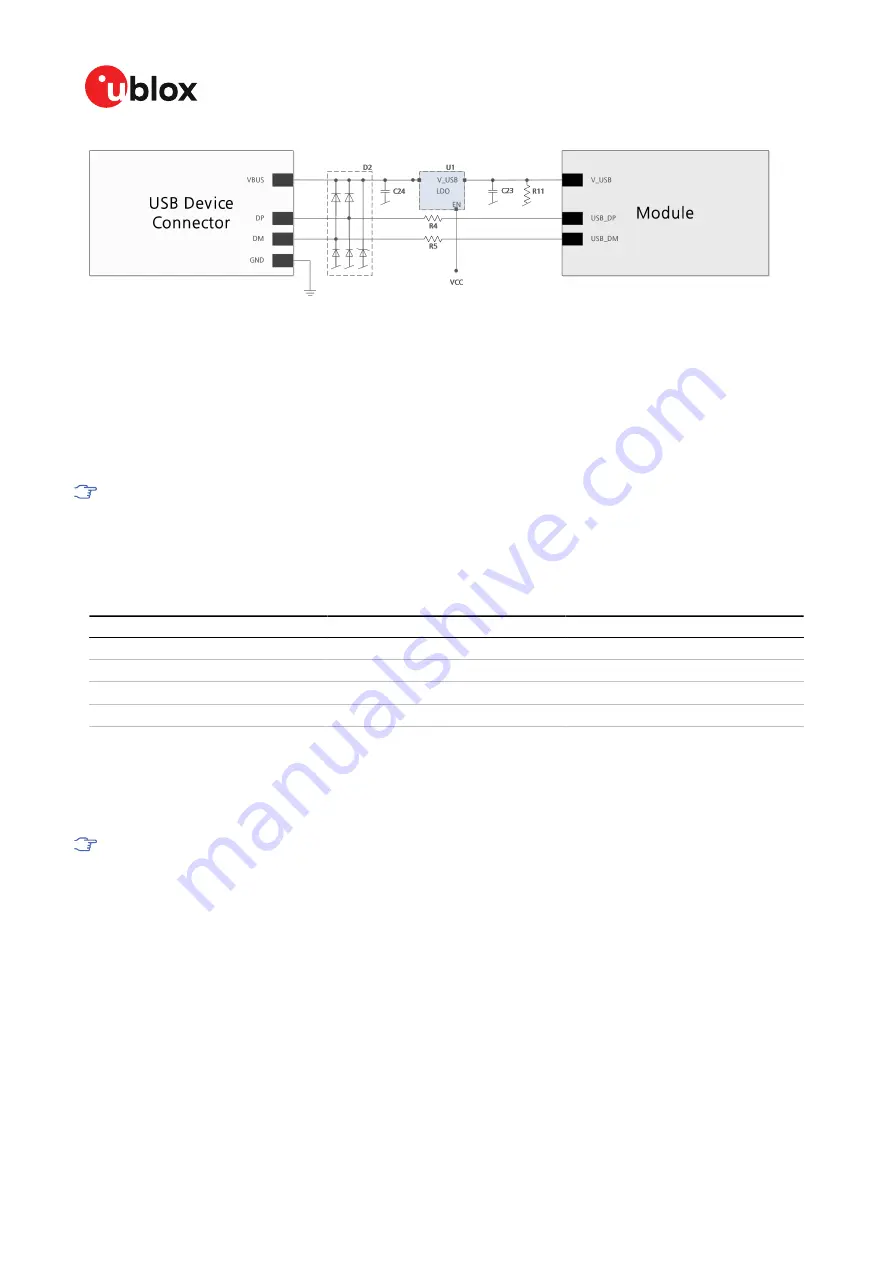

Figure 17: ZED-F9K example circuit for USB interface

R11 = 100 k Ω is recommended

R4, R5 = 27 Ω is recommended

3.5 Predefined PIOs

In addition to the communication ports, there are some predefined PIOs provided by ZED-F9K to

interact with the receiver. These PIOs are described in this chapter.

If hardware backup mode is used a proper isolation of the interfaces is needed.

3.5.1 D_SEL

The D_SEL pin can be used to configure the functionality of the combined UART1, I2C, and SPI pins.

It is possible to configure the pins as UART1 + I2C, or as SPI. SPI is not available unless D_SEL pin

is set to low. See

Pin no.

D_SEL == 0

D_SEL == 1

42

SPI_MISO

UART1 TXD

43

SPI_MOSI

UART1 RXD

44

SPI_CS_N

I2C SDA

45

SPI_CLK

I2C SCL

Table 16: D_SEL configuration

3.5.2 RESET_N

The ZED-F9K provides the ability to reset the receiver. The RESET_N pin is an input-only pin with an

internal pull-up resistor. Driving RESET_N low for at least 100 ms will trigger a cold start.

The RESET_N pin will delete all information and trigger a cold start. It should only be used

as a recovery option.

3.5.3 SAFEBOOT_N

The ZED-F9K provides a SAFEBOOT_N pin that is used to command the receiver safe boot mode.

If this pin is low at power up, the receiver starts in safe boot mode and GNSS operation is disabled.

The safe boot mode can be used to recover from situations where the flash content has become

corrupted and needs to be restored.

In safe boot mode the receiver runs from a passive oscillator circuit with less accurate timing and

hence the receiver is unable to communicate via USB.

In this mode only UART1 , I2C or SPI communication is possible. For communication via UART1 in

safe boot mode, the host must send a training sequence (0 x 55 55 at 9600 baud) to the receiver in

order to begin communication. After this the host must wait at least 2 ms before sending any data.

UBX-20046189 - R01

3 Receiver functionality

Page 41 of 105

C1-Public

Early production information