LEA-M8F - Hardware Integration Manual

UBX-14000034 - R03

Early Production

Information

Hardware

description

Page 9 of 30

1.5.2.1

USB external components

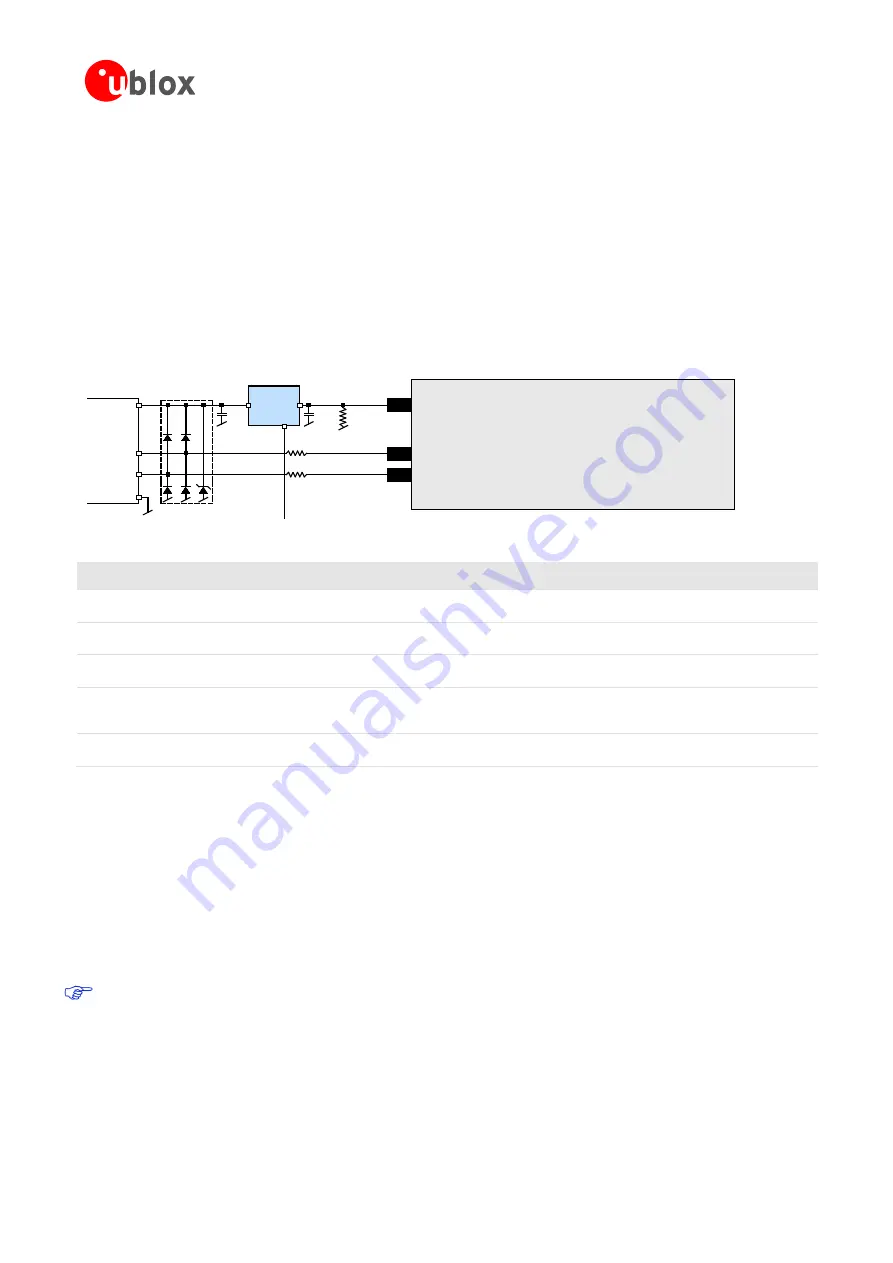

The USB interface requires some external components to comply with the USB 2.0 specification. These are

shown below in Figure 2 and listed in Table 2. To comply with USB specifications, VBUS must be connected

through an LDO (U1) to pin 24 (

VDD_USB)

to regulate the 5 V VBUS down to a nominal 3.3 V for the module.

The LEA-M8F module USB interface is intended to be used as a USB

self-powered

device deriving its power

supply from

VCC.

However, the module power supply (

VCC

) can be turned off independently of the host VBUS

supplying VDD_USB. With VDD_USB active, the USB host would receive a signal indicating that the device is

present and ready to communicate. This should be avoided by disabling the LDO (U1) using the enable signal

(EN) of the VCC-LDO enabled by e.g.

VCC

. Depending on the characteristics of the LDO (U1) it is recommended

to add a pull-down resistor (R11) at its output to ensure

VDD_USB

is not floating if the LDO (U1) is disabled or

the USB cable is disconnected i.e. VBUS is not supplied.

Module

VDD_USB

LDO

VDD_USB

R4

USB_DP

USB_DM

R5

C24

C23

D2

VBUS

DP

DM

GND

US

B D

evi

ce Co

nn

ec

to

r

U1

EN

R11

EN

Figure 2: USB Interface

Name Component Function

Comments

U1

LDO

Regulates VBUS (4.4 …5.25 V)

down to a voltage of 3.3 V.

Almost no current requirement (~1 mA) if the GNSS receiver is operated as a

USB self-powered device.

C23,

C24

Capacitors

Required according to the specification of LDO U1

D2

Protection

diodes

Protect circuit from overvoltage

/ ESD when connecting.

Use low capacitance ESD protection such as ST Microelectronics USBLC6-2.

R4, R5

Serial

termination

resistors

Establish a full-speed driver

impedance of 28…44

Ω

A value of 27

Ω

is recommended.

R11

Resistor

100 k

Ω

is recommended for USB self-powered setup. For bus-powered setup,

R11 can be ignored.

Table 2: Summary of USB external components

1.5.3

Display Data Channel (DDC)

An I

2

C compatible Display Data Channel (DDC) interface is available for serial communication with an external

host CPU. The interface only supports slave mode operation (master mode is not supported). The DDC protocol

and electrical interface are fully compatible with the Fast-Mode of the I

2

C industry standard. The DDC pins

SDA

and

SCL

have internal 10 k

Ω

pull-up resistors.

For more information about the DDC implementation, see the

u-blox M8 Receiver Description Including Protocol

[2]. For bandwidth information, see the

LEA-M8F Data Sheet

[1]. For timing, parameters consult the

I

2

C-bus specification

The u-blox M8 DDC interface supports serial communication with u-blox cellular modules. See the

specification of the applicable cellular module to confirm compatibility.

1.5.4

SPI

An SPI interface is available for communication to a host CPU, however its interface connections are shared with

the UART and DDC interface pins. The SPI interface is not available in the default configuration but can be