TXZ+ Family

TMPM4G Group(1)

Clock Control and Operation Mode

2021-06-30

Rev. 1.1

72 / 88

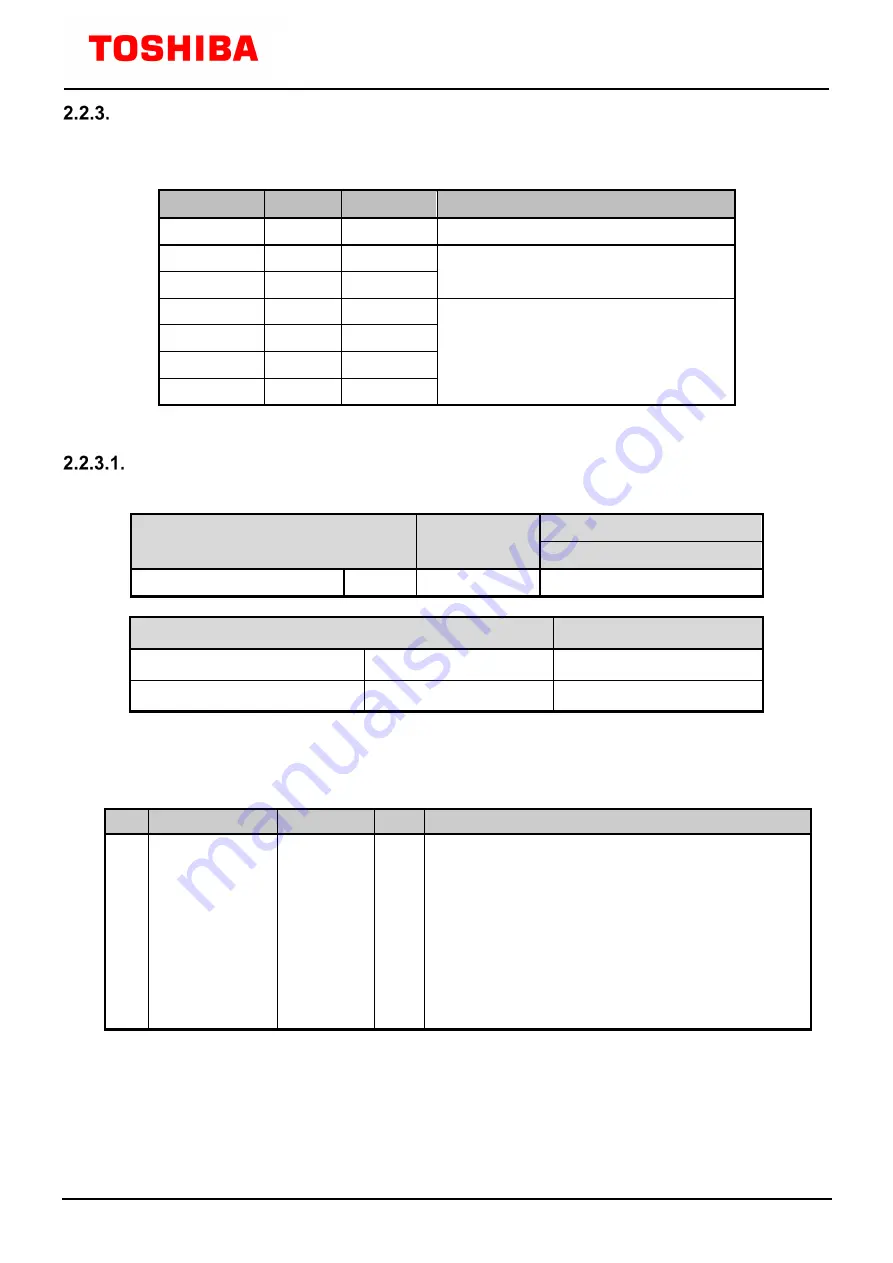

RAM Access

The number of clocks required to access the internal RAM is shown in the table below.

Table 2.10 The number of clocks to access each RAM

RAM

fsys

Clock

description

RAM0

fsysh

1

-

RAM1

fsysh

1 or 2

Refer to “2.2.3.1 Control Registers”.

RAM2

fsysh

1 or 2

RAM3

fsysm

1

Access between the high speed domain and

the middle speed domain requires

synchronization time between domains.

RAM4

fsysm

1

RAM5

fsysm

1

Backup RAM

fsysm

5

Control Registers

Change the setting according to the fsysh frequency.

Peripheral Function

Channel/Unit

Base Address

Type 1

-

FC

-

0x5DFF0000

Register Name

Address(Base+)

Flash Key Code Register (Note)

[FCKCR]

0x0018

RAM Access Control Register

[FCRACCR]

0x1218

Note: This register is same as the register of the reference manual “Flash memory”

[FCKCR]

(Flash Key Code Register)

Bit

Bit Symbol

After reset

Type

Function

31:0

KEYCODE

0x00000000

W

Locked register release key code

When

[FCRACCR]

is rewritten, write the specific code

(0xA74A9D23) to this register. And then rewrite the

value of the register within 16 clocks after the previous

action.

If valid data is written to this register within 16 clocks,

released status is reset.