22.3.4.2 Flash Memory Chip Erase and Protect Bit Erase

Flash memory chip erase and protect bit erase commands erase the entire blocks of Flash memory and

write/erase protects of all blocks regardless of write/erase protect or security status.

22.3.5 Common Operation regardless of Command

This section describes common operation under the boot program execution.

22.3.5.1 Serial Operation Mode Determination

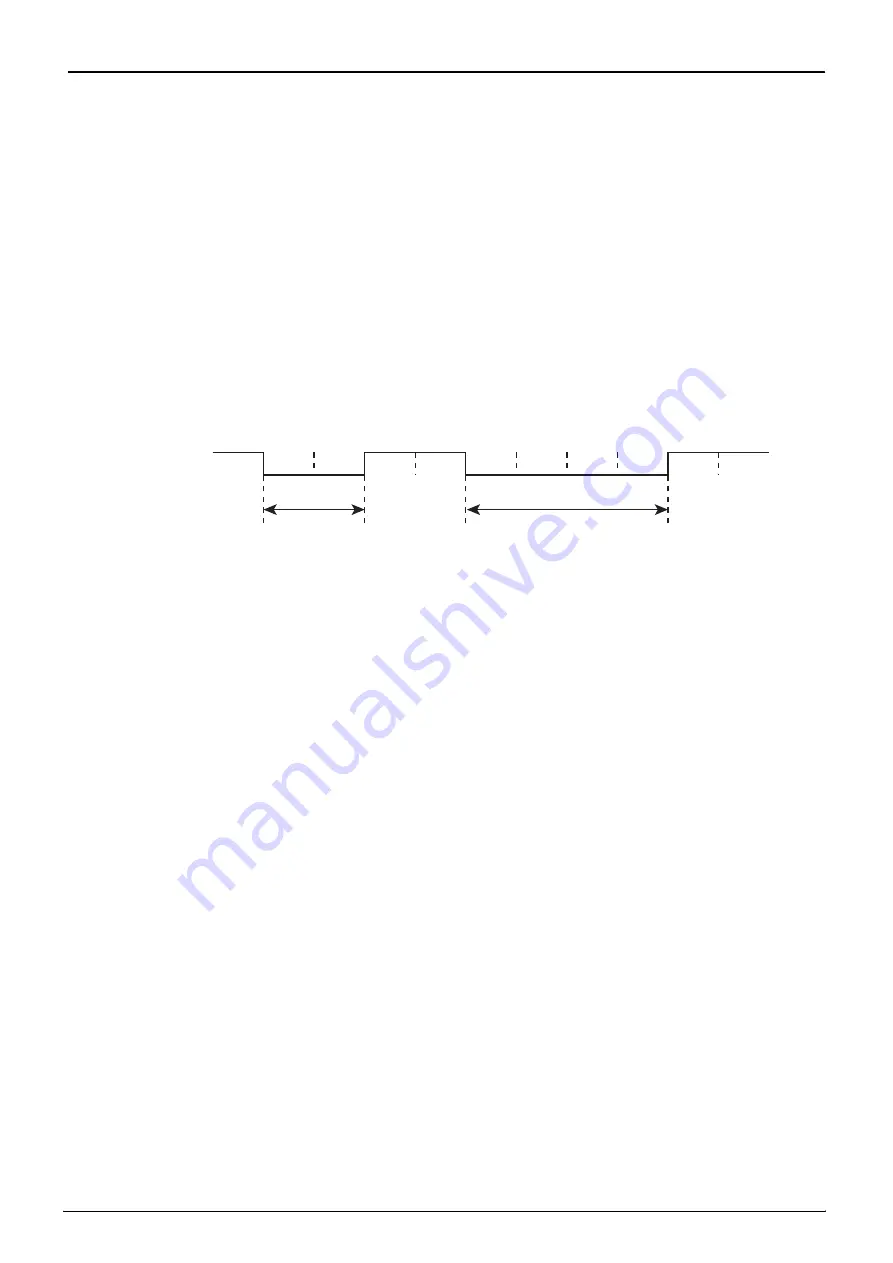

When the controller communicates via UART, set the 1st byte to 0x86 at the desired baud rate. Figure

22-8shows waveforms .

UART (0x86)

tAB

Point A

Start

bit 0

bit 1

bit 2

bit 3

bit 4

bit 5

bit 6

bit 7

Stop

Point B

Point C

Point D

tCD

Figure 22-8 Serial operation mode determination data

Figure 22-9 shows a flowchart of boot program. Using 16-bit timer (TMRB) with the time of tAB,

tAC and tAD, the 1st byte of serial operation mode determination data (0x86) after reset is provided. In Fig-

ure 22-9, the CPU monitors level of the receive pin, and obtains a timer value at the moment when the re-

ceive pin’s level is changed. Consequently, the timer values of tAB, tAC and tAD have a margin of er-

ror. In addition, note that if the transfer goes at a high baud rate, the CPU may not be able to determine

the level of receive pin.

The flowchart in Figure 22-10 shows the serial operation mode is determined that the time length of

the receive pin is long or short. If the length is tAB ≤ tCD, the serial operation mode is determined as

UART mode. The time of tAD is used whether the automatic baud rate setting is enable or not. Note that

timer values of tAB, tAC and tAD have a margin of error. If the baud rate is high and operation frequen-

cy is low, each timer value becomes small. This may generates unexpected determination occurs. (To pre-

vent this problem, re-set UART within the programming routine.)

For example, When UART mode is utilized, the controller should allow for a time-out period where

the time is expected to receive an echo-back (0x86) from the target board. The controller should give up

the communication if it fails to get that echo-back within the allowed time.

TMPM3V6/M3V4

22.

Flash Memory Operation

22.3 How to Reprogram Flash using Single Boot Mode

Page 466

2019-02-06

Summary of Contents for TMPM3V4

Page 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Page 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Page 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Page 8: ......

Page 22: ...xiv ...

Page 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Page 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Page 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Page 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Page 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Page 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Page 544: ......