Page 93

TMP86PM29BUG

9.3.5

16-Bit Timer Mode (TC3 and 4)

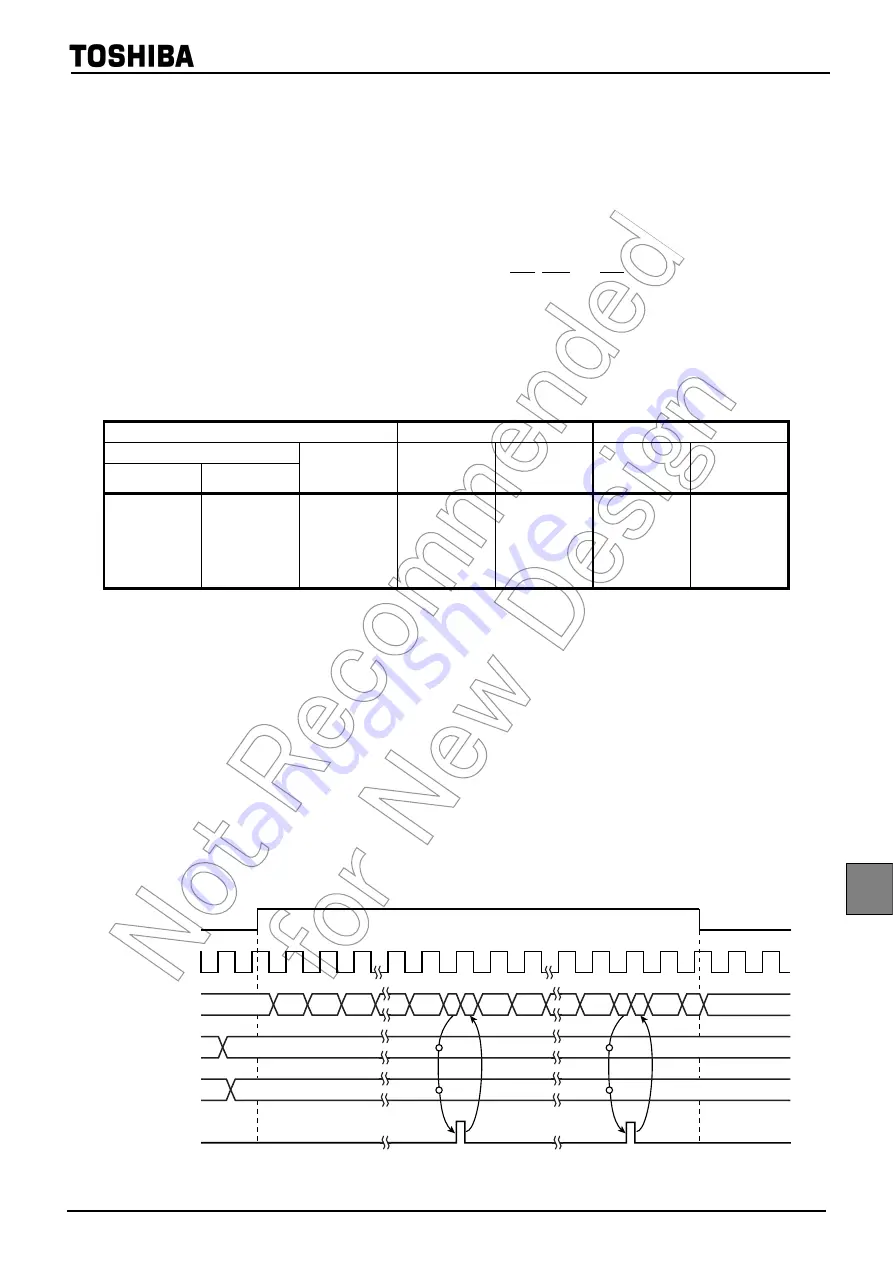

In the timer mode, the up-counter counts up using the internal clock. The TimerCounter 3 and 4 are cascad-

able to form a 16-bit timer.

When a match between the up-counter and the timer register (TTREG3, TTREG4) value is detected after the

timer is started by setting TC4CR<TC4S> to 1, an INTTC4 interrupt is generated and the up-counter is cleared.

After being cleared, the up-counter continues counting. Program the lower byte and upper byte in this order in

the timer register. (Programming only the upper or lower byte should not be attempted.)

Note 1: In the timer mode, fix TCjCR<TFFj> to 0. If not fixed, the

PDOj

,

PWMj

, and

PPGj

pins may output a pulse.

Note 2: In the timer mode, do not change the TTREGj setting while the timer is running. Since TTREGj is not in the

shift register configuration in the timer mode, the new value programmed in TTREGj is in effect immediately

after programming of TTREGj. Therefore, if TTREGj is changed while the timer is running, an expected

operation may not be obtained.

Note 3: j = 3, 4

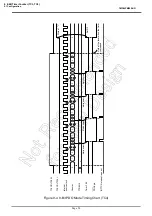

Figure 9-6 16-Bit Timer Mode Timing Chart (TC3 and TC4)

Table 9-6 Source Clock for 16-Bit Timer Mode

Source Clock

Resolution

Maximum Time Setting

NORMAL1/2, IDLE1/2 mode

SLOW1/2,

SLEEP1/2

mode

fc = 16 MHz

fs = 32.768 kHz

fc = 16 MHz

fs = 32.768 kHz

DV7CK = 0

DV7CK = 1

fc/2

11

fs/2

3

fs/2

3

128

µ

s

244.14

µ

s

8.39 s

16 s

fc/2

7

fc/2

7

–

8

µ

s

–

524.3 ms

–

fc/2

5

fc/2

5

–

2

µ

s

–

131.1 ms

–

fc/2

3

fc/2

3

–

500 ns

–

32.8 ms

–

Example :Setting the timer mode with source clock fc/2

7

Hz, and generating an interrupt 300 ms later

(fc = 16.0 MHz)

LDW

(TTREG3), 927CH

: Sets the timer register (300 ms

÷

2

7

/fc = 927CH).

DI

SET

(EIRH). 3

: Enables INTTC4 interrupt.

EI

LD

(TC3CR), 13H

:Sets the operating clock to fc/2

7

, and 16-bit timer mode

(lower byte).

LD

(TC4CR), 04H

: Sets the 16-bit timer mode (upper byte).

LD

(TC4CR), 0CH

: Starts the timer.

1

0

2

3

mn-1

mn

0

1

mn-1

mn

2

0

1

2

0

n

?

m

?

Internal

source clock

Counter

Match

detect

Counter

clear

Match

detect

Counter

clear

TC4CR<TC4S>

TTREG3

(Lower byte)

INTTC4 interrupt request

TTREG4

(Upper byte)

Summary of Contents for TLCS-870/C Series

Page 1: ...8 Bit Microcontroller TLCS 870 C Series TMP86PM29BUG ...

Page 6: ...TMP86PM29BUG ...

Page 7: ...Revision History Date Revision 2007 10 11 1 First Release 2008 8 29 2 Contents Revised ...

Page 9: ......

Page 15: ...vi ...

Page 19: ...Page 4 1 3 Block Diagram TMP86PM29BUG 1 3 Block Diagram Figure 1 2 Block Diagram ...

Page 23: ...Page 8 1 4 Pin Names and Functions TMP86PM29BUG ...

Page 48: ...Page 33 TMP86PM29BUG ...

Page 49: ...Page 34 2 Operational Description 2 3 Reset Circuit TMP86PM29BUG ...

Page 61: ...Page 46 3 Interrupt Control Circuit 3 8 External Interrupts TMP86PM29BUG ...

Page 81: ...Page 66 6 Watchdog Timer WDT 6 3 Address Trap TMP86PM29BUG ...

Page 135: ...Page 120 10 8 Bit TimerCounter TC5 TC6 10 1 Configuration TMP86PM29BUG ...

Page 145: ...Page 130 11 Asynchronous Serial interface UART 11 9 Status Flag TMP86PM29BUG ...

Page 165: ...Page 150 13 10 bit AD Converter ADC 13 6 Precautions about AD Converter TMP86PM29BUG ...

Page 183: ...Page 168 15 LCD Driver 15 4 Control Method of LCD Driver TMP86PM29BUG ...

Page 201: ...Page 186 18 Electrical Characteristics 18 9 Handling Precaution TMP86PM29BUG ...

Page 203: ...Page 188 19 Package Dimensions TMP86PM29BUG ...

Page 205: ......