69

SLOS743L – AUGUST 2011 – REVISED MARCH 2017

Product Folder Links:

Detailed Description

Copyright © 2011–2017, Texas Instruments Incorporated

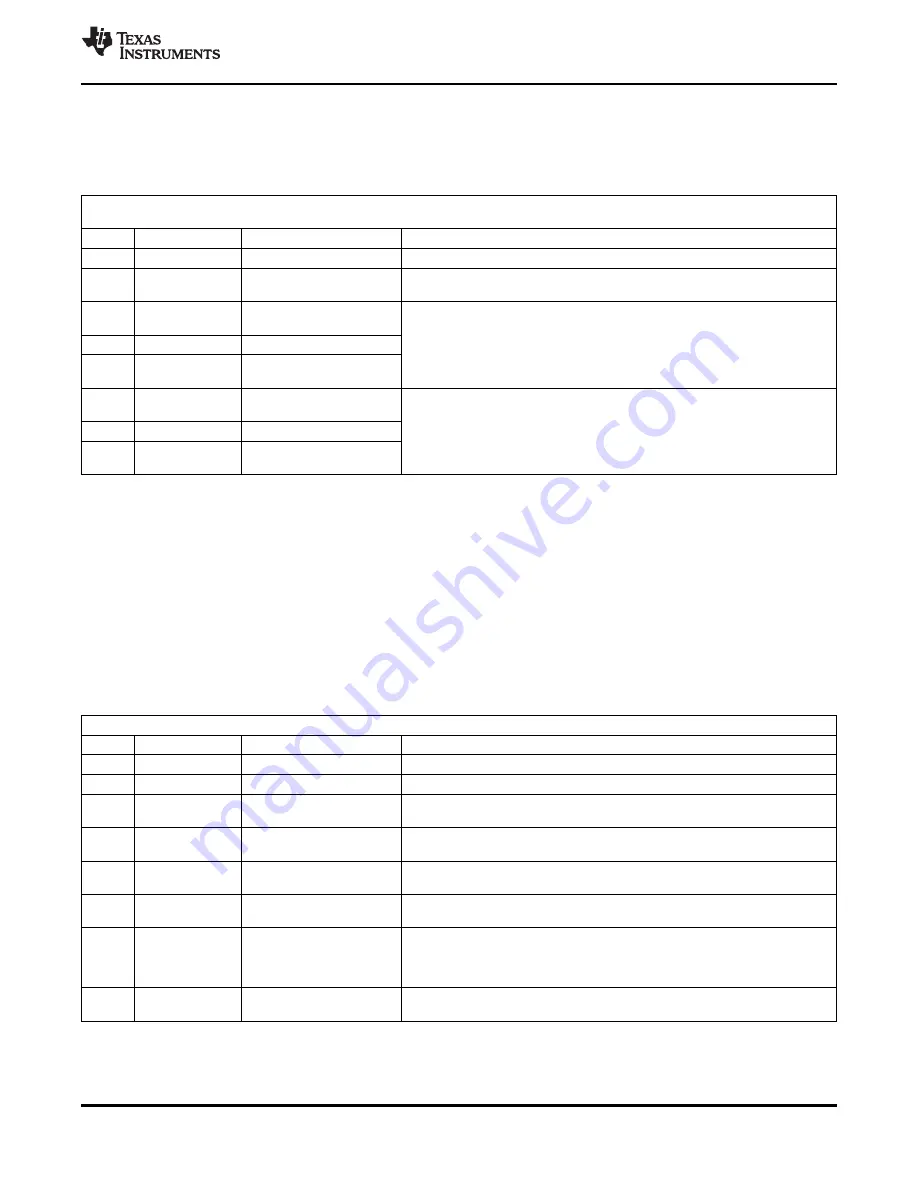

6.15.3.3.3 RSSI Levels and Oscillator Status Register (0x0F)

describes the RSSI Levels and Oscillator Status register.

Table 6-47. RSSI Levels and Oscillator Status Register (0x0F)

Function:

Displays the signal strength on both reception channels and RF amplitude during RF-off state. The RSSI values are valid from

reception start till start of next transmission.

Bit

Name

Function

Description

B7

Unused

B6

osc_ok

Crystal oscillator stable

indicator

13.56-MHz frequency stable (approximately 200 µs)

B5

rssi_x2

MSB RSSI value of auxiliary

RX (RX_IN2)

Auxiliary channel is by default RX_IN2. The input can be swapped by B3 = 1

(Chip Status Control register 0x00). If "swapped", the Auxiliary channel is

connected to RX_IN1 and, hence, the Auxiliary RSSI represents the signal level

at RX_IN1.

B4

rssi_x1

Auxiliary channel RSSI

B3

rssi_x0

MSB RSSI value of auxiliary

RX (RX_IN2)

B2

rssi_2

MSB RSSI value of main

RX (RX_IN1)

Active channel is default and can be set with option bit B3 = 0 of Chip Status

Control register 0x00.

B1

rssi_1

Main channel RSSI

B0

rssi_0

LSB RSSI value of main RX

(RX_IN1)

RSSI measurement block is measuring the demodulated envelope signal (except in case of direct

command for RF amplitude measurement described later in direct commands section). The measuring

system is latching the peak value, so the RSSI level can be read after the end of receive packet. The

RSSI value is reset during next transmit action of the reader, so the new tag response level can be

measured. The RSSI levels calculated to the RF_IN1 and RF_IN2 are presented in

and

. The RSSI has 7 steps (3 bits) with 4-dB increment. The input level is the peak-to-peak

modulation level of RF signal measured on one side envelope (positive or negative).

6.15.3.3.4 Special Functions Register (0x10)

describes the Special Functions register at address 0x10.

Table 6-48. Special Functions Register (0x10)

Function:

User configurable options for ISO/IEC 14443 A specific operations

Bit

Name

Function

Description

B7

Reserved

Reserved

B6

Reserved

Reserved

B5

par43

Disables parity checking for

ISO/IEC 14443 A

B4

next_slot_37us

0 = 18.88 µs

1 = 37.77 µs

Sets the time grid for next slot command in ISO/IEC 15693

B3

Sp_dir_mode

Bit stream transmit for

MIFARE at 106 kbps

Enables direct mode for transmitting ISO/IEC 14443 A data, bypassing the

FIFO and feeding the data bit stream directly onto the encoder.

B2

4_bit_RX

0 = normal receive

1 = 4-bit receive

Enable 4-bit replay for example, ACK, NACK used by some cards; for example,

MIFARE Ultralight

B1

14_anticoll

0 = anticollision framing

(0x93, 0x95, 0x97)

1 = normal framing (no

broken bytes)

Disable anticollision frames for ISO/IEC 14443 A (this bit should be set to 1

after anticollision is finished)

B0

col_7_6

0 = 7 subcarrier pulses

1 = 6 subcarrier pulses

Selects the number of subcarrier pulses that trigger collision error in

ISO/IEC 14443 A at 106 kbps