Introduction

3

SLVUBT0 – December 2019

Copyright © 2019, Texas Instruments Incorporated

TPS6594x-Q1 Evaluation Module

1

Introduction

The TPS65941x-Q1 power management integrated circuit (PMIC) family is extremely flexible and scalable,

providing configurability at the device and system level. At the device level, a single PMIC can provide up

to five separate step down converters (BUCK regulators) and four LDOs. Four of these BUCK regulators

can be used in multi-phase mode to provide a single 14A source. At the system level, several PMICs can

be configured to work in a master-slave topology with one master and up to five slave PMICs. The

TPS65941x-Q1 evaluation module (EVM) is both an evaluation and development tool. With the EVM both

device level and system level configurability are available through an easy to use graphical user interface

(GUI) tool.

shows the available master and slave EVMs, the silicon associated with those EVMs, the initial

non-volatile memory (NVM) configuration, and the hardware components associated with the

configurations. Because of the configurable nature of both the part and the EVM, any EVM can be

configured as a master or slave device. Master and slave configurations are provided to facilitate getting

started and to accelerate development.

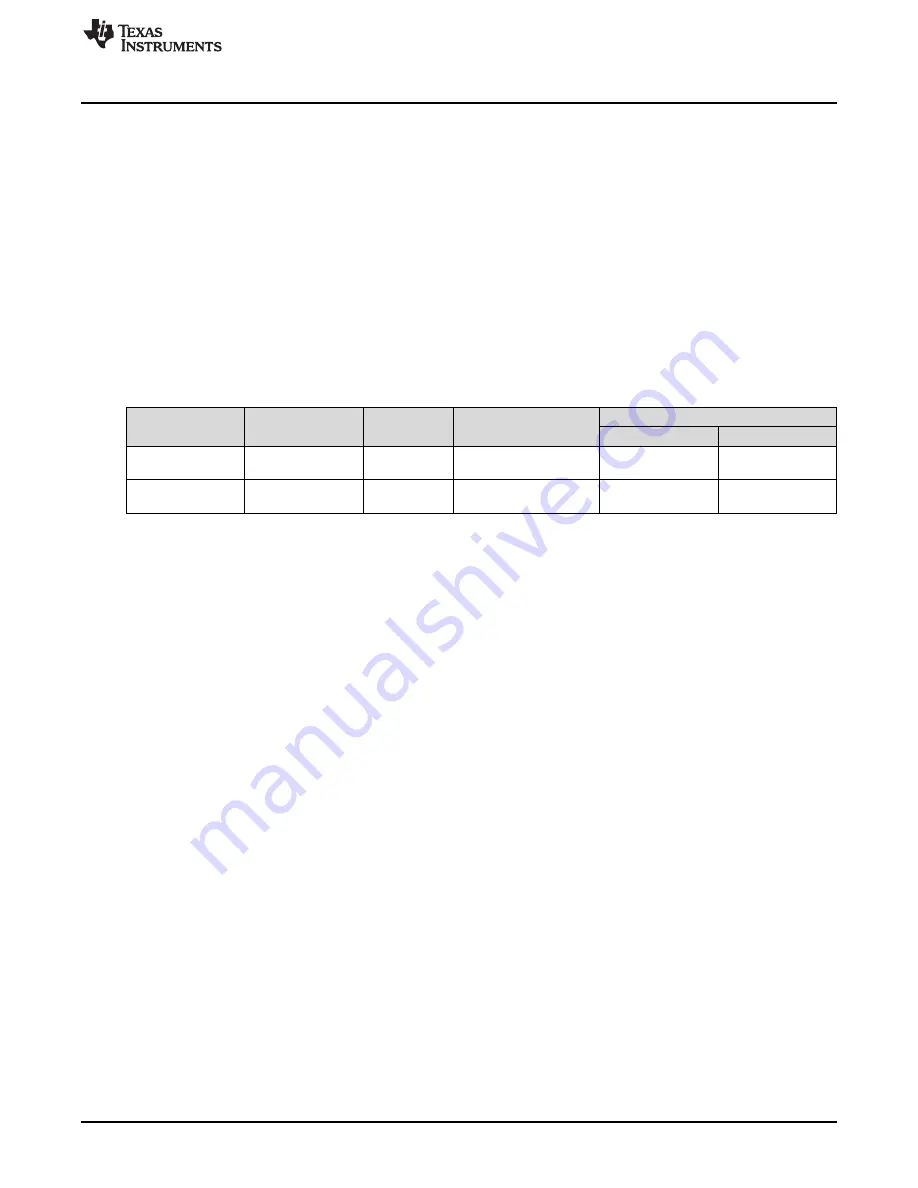

Table 1. EVM Descriptions

EVM Part Number

PMIC Device Part

Number

Mode

NVM Phase

Configuration

Components on the Back Side of EVM

R1-R7

J23,J24,J25

TPS659413EVM

PTPS659413F0RW

ERQ1

Master

BUCK1+BUCK2, BUCK3,

BUCK4, and BUCK5

R1,R2,R5, and R7

J23

TPS659411EVM

PTPS659411F0RW

ERQ1

Slave

BUCK1+BUCK2+BUCK3

+BUCK4, and BUCK5

R1,R2,R4,and R6

J23,J24, and J25

2

Getting Started

Only a power supply and the EVM are required to evaluate and test the TPS6594x-Q1 default

configuration under load conditions. This section contains the master and slave configurations and

how to run these two default configurations.

2.1

Getting Started: Single EVM

1. Connect Power to the EVM.

2. Connect the EVM to the Host PC through the USB. In the event that the power is provided by the USB

cable, apply the appropriate jumper connection to connect VBUS and VSYS see

3. Launch the GUI and evaluate.

Terminal J6, labeled VSYS_IN in

, can accept wire gauges up to 14 AWG. The voltage supplied

must be within the input range of the device, 2.7 V to 5.5 V. The power supply providing the input to

VSYS_IN is required to supply 120% of the output power. Once power has been supplied to VSYS_IN, the

pullup on nPWRON/ENABLE pin will enable the device and the power output rails will activate. The

default ON Request for the master device is the ENABLE pin which is a level sensitive input. Please refer

to

for more details.

shows the TPS659413EVM (master).