206

TMS320C6670 Peripheral Information and Electrical Specifications

Copyright 2012 Texas Instruments Incorporated

SPRS689D—March 2012

Multicore Fixed and Floating-Point System-on-Chip

TMS320C6670

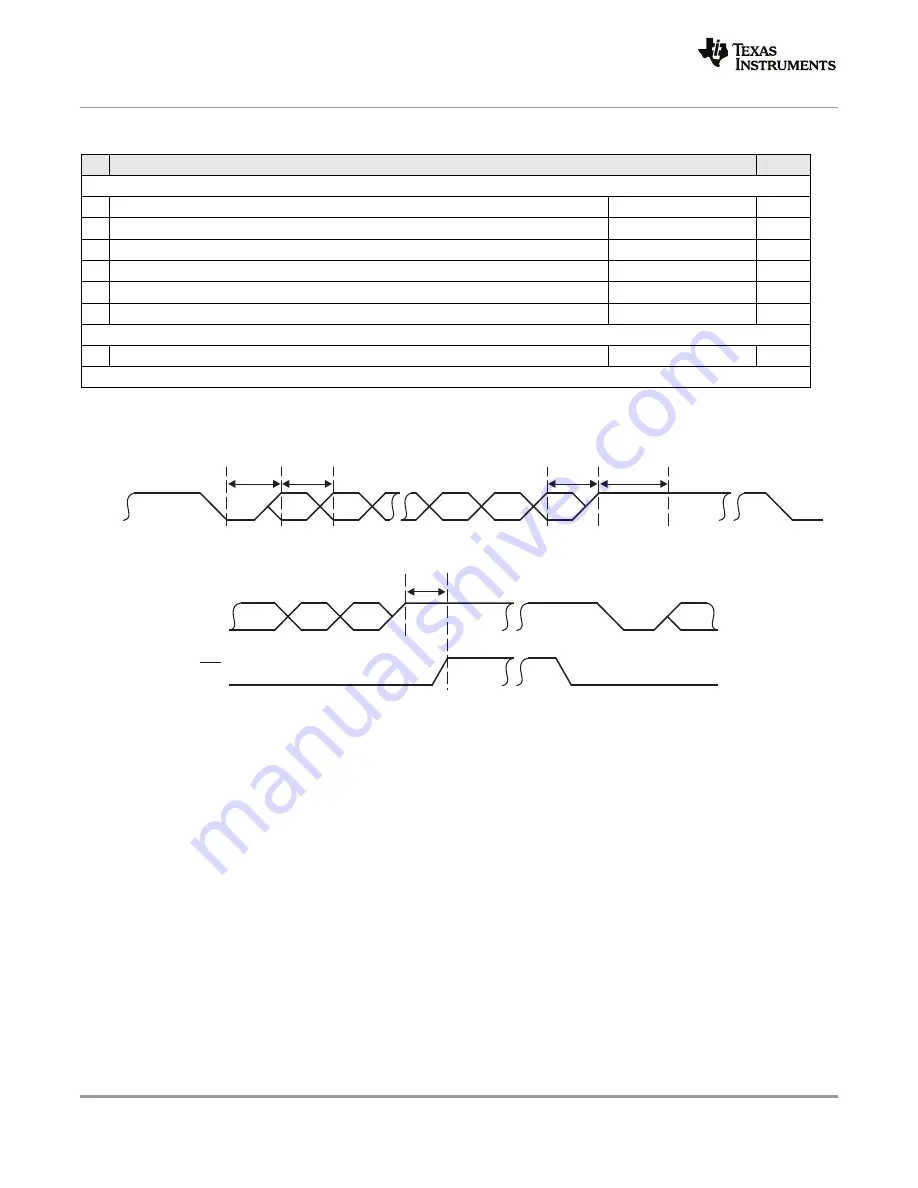

Figure 7-45

UART Transmit Timing Waveform

Figure 7-46

UART RTS (Request-to-Send Output) – Autoflow Timing Waveform

7.16 PCIe Peripheral

The 2-lane PCI express (PCIe) module on TMS320C6670 provides an interface between the SoC and other

PCIe-compliant devices. The PCI express module provides low pin-count, high-reliability, and high-speed data

transfer at rates of 5.0 Gbps per lane on the serial links. For more information, see the

Peripheral Component

Interconnect Express (PCIe) for KeyStone Devices User Guide

in

2.9 ‘‘Related Documentation from Texas

7.17 Packet Accelerator

The Packet Accelerator provides L2 to L4 classification functionalities. It supports classification for Ethernet, VLAN,

MPLS over Ethernet, IPv4/6, GRE over IP, and other session identification over IP such as TCP and UDP ports. It

maintains 8k multiple-in, multiple-out hardware queues. It also provides checksum capability as well as some QoS

capabilities. It enables a single IP address to be used for a multi-core device. It can process up to 1.5 Mpps. The Packet

Accelerator is coupled with the Network Coprocessor. For more information, see the

Packet Accelerator (PA) for

KeyStone Devices User Guide

in

2.9 ‘‘Related Documentation from Texas Instruments’’ on page 66

.

Table 7-73

UART Switching Characteristics

)

No.

Parameter

Min

Max

Unit

Transmit Timing

1

tw(TXSTART)

Pulse width, transmit start bit

U

(1)

- 2

1 U = UART baud time = 1/programmed baud rate

U + 2

ns

2

tw(TXH)

Pulse width, transmit data/parity bit high

U - 2

U + 2

ns

2

tw(TXL)

Pulse width, transmit data/parity bit low

U - 2

U + 2

ns

3

tw(TXSTOP1)

Pulse width, transmit stop bit 1

U - 2

U + 2

ns

3

tw(TXSTOP15)

Pulse width, transmit stop bit 1.5

1.5 * (U - 2) 1.5 * ('U + 2)

ns

3

tw(TXSTOP2)

Pulse width, transmit stop bit 2

2 * (U - 2)

2 * ('U + 2)

ns

Autoflow Timing Requirements

7

td(RX-RTSH)

Delay time, STOP bit received to RTS deasserted

P

(2)

2 P = 1/SYSCLK7

5P

ns

End of Table 7-73

3

2

2

1

Stop/Idle

T

X

D

Start

Bit 0

Bit 1

Bit N-1

Bit N

Parit

y

Stop

Idle

Start

7

R

X

D

Bit N-1

Bit N

Stop

Start

CTS

Summary of Contents for TMS320C6670

Page 225: ......