2.2

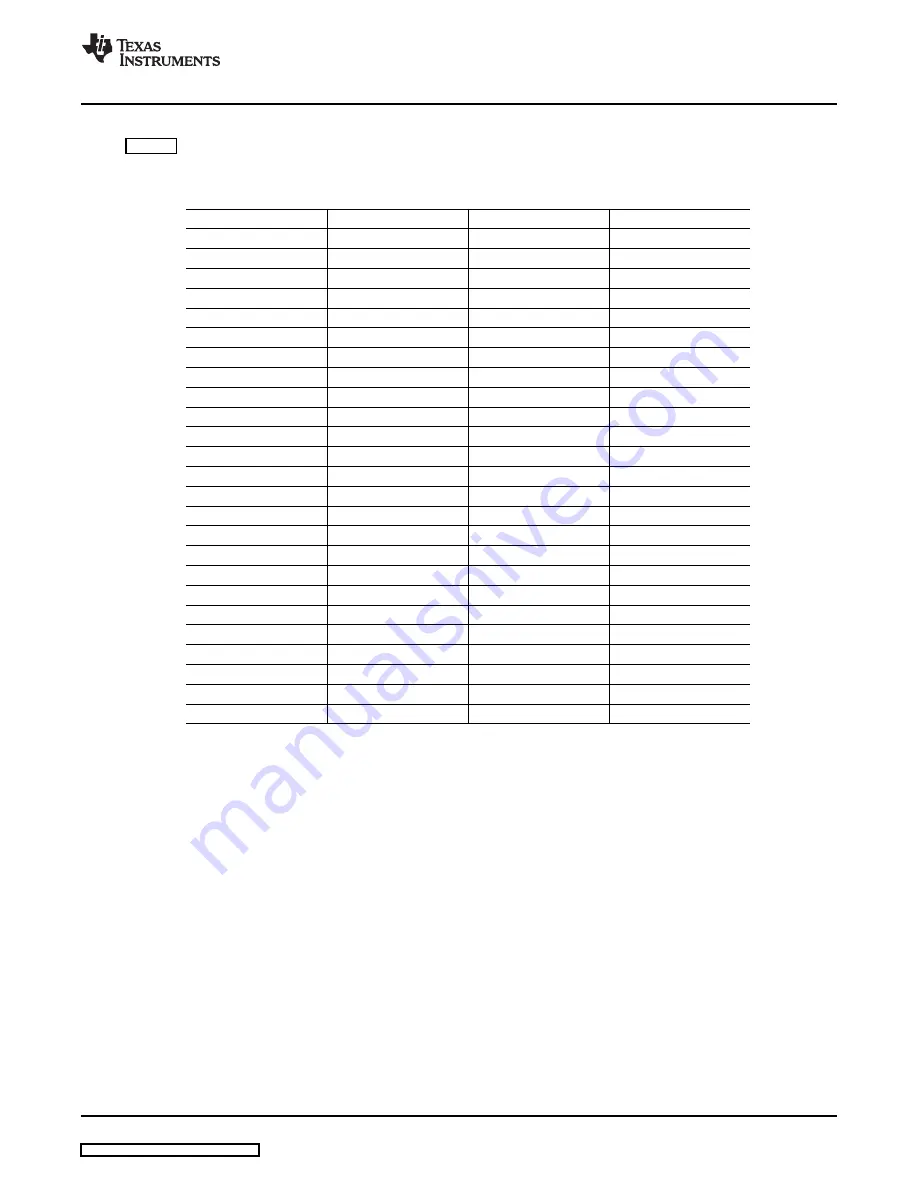

Signal Definitions of J1 (25-Pin Male DSUB)

www.ti.com

System Setup

lists the different signals connected to J1 on the PGA112_Test_Board. This table also identifies

signals connected to pins on J1 that are not used on the GA112_Test_Board.

Table 1. Signal Definition of J1 (25-Pin Male DSUB) on PGA112_Test_Board

J1 Pin

Signal

Used On This EVM?

PGA112 Pin

1

DAC A

Yes

DAC1

2

DAC B

Yes

DAC2

3

DAC C

Yes

DAC3

4

DAC D

Yes

V

REF

_DAC

5

ADS1+

Yes

ADS1+

6

ADS1–

Yes

ADS1–

7

ADS2+

Yes

ADS2+

8

ADS2–

Yes

ADS2–

9

I2C_SCK

No

—

10

I2C_SDA2

No

—

11

ONE_WIRE

No

—

12

I2C_SCK_ISO

No

—

13

I2C_SDA_ISO

No

—

14

X

No

—

15

XTR_LOOP–

No

—

16

INA–

No

—

17

V

DUT

Yes

V

DUT

18

V

CC

No

V

CC

19

+15V

No

—

20

–15V

No

—

21

GND

Yes

GND

22

SPI_SCK

Yes

SPI_SCK

23

SPI_CS1

Yes

SPI_CS1

24

SPI_DOUT

Yes

SPI_DOUT

25

SPI_DIN1

Yes

SPI_DIN1

SBOU073 – February 2009

PGA112 Evaluation Module

7