© Texas Instruments 2011

www.ti.com

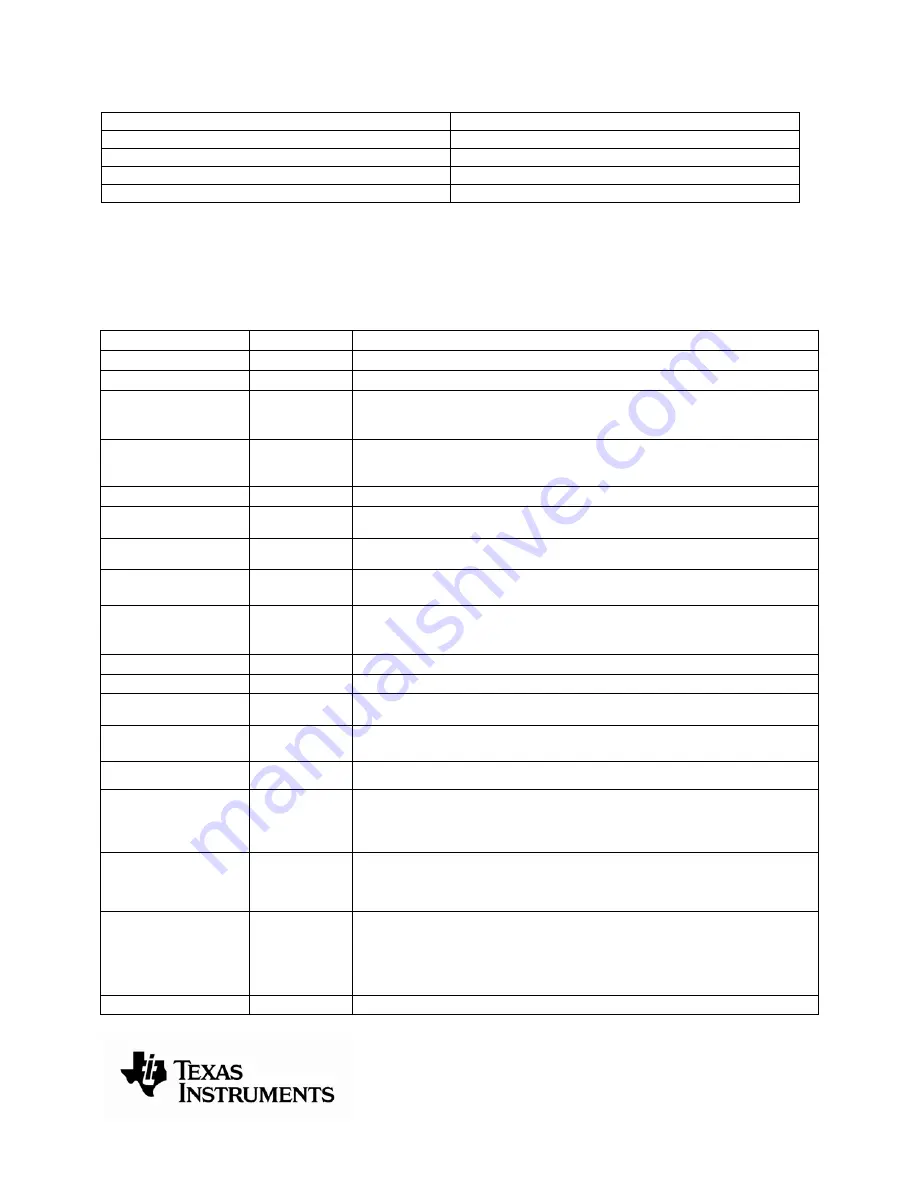

Table 1. Switches to set the 4-level input control pins

4 – level Input Settings

Setting for 3 pin switches (3-2-1)

0 – Tie 249 ohm to GND

ON

– OFF – OFF

R – Tie 5k ohm to GND

OFF –

ON

– OFF

F – FLOAT (open)

OFF – OFF – OFF

1 – Tie 249 ohm to VIH

OFF – OFF –

ON

The following switches are used to set the input condition for the 4-level inputs:

SW1, SW2, SW3, SW5, SW6, SW10, SW11.

There are 3 switches connected to an input signal pin. Each switch when set to the ON position sets the pin to

one of the 4-level setting. The 6 pin switches are assigned similar to the 3 pin switches. The only difference is 2

signal pins are connected and thus 6-5-4 is for the one signal pin and 3-2-1 is for another signal pin. Please note

only 1 switch at the ON position is allowed.

Table 2. Connection and Control Description

Component

Name

Function

J1

PCIE TX/RX

High speed differential TX/RX from/to Root Complex

J2

PCIE TX/RX

High speed differential TX/RX to/from End Point

J3, J5

3.3V to VIN

3.3V DC Power – VIN to DS80PCI800SQ

Jumper ON = 3.3V mode operation

Jumper OFF = 2.5V mode operation

J4, J6

2.5V to VDD

2.5V DC Power – VDD to DS80PCI800SQ

Jumper ON (1-2, 3-4) = 2.5V mode operation

Jumper OFF (1-2, 3-4) = 3.3V mode operation

J7

VIN or VDD

Jumper VIH: set 1-2 = VIN (3.3V) or set 2-3 = VDD (2.5V)

J8 SDA,

SCL

Optional SMBUS access pins.

See the datasheet for additional information on SMBUS.

J9

EEPROM

Optional socket for EEPROM

SW1

EQB[1:0] or

AD[3:2]

PIN MODE – EQ control for channel B inputs

SMBUS MODE – AD[3:2] device address bits

SW2

ENSMB

ENSMB = LOW – PIN MODE

ENSMB = HIGH – SMBUS (slave mode)

ENSMB = FLOAT – SMBUS (master mode – load configuration from EEPROM)

SW3

DEMA[1:0]

PIN MODE – DE control for channel A outputs

SW4

SDA/SCL

“ON” position connects SDA and SCL lines to the device pin.

SW5

DEMB[1:0] or

AD[1:0]

PIN MODE – DE control for channel B outputs

SMBUS MODE – AD[1:0] device address bits

SW6

SD_TH and

LPBK - RES

SD_TH – Signal detect threshold level (FLOAT = Default level)

LPBK function for PCI402 and RESERVED for PCI800 (FLOAT = Normal operation)

SW7

VDD_SEL1_2

VDD_SEL3_4

VDD_SEL – Enable or disable the internal 3.3V to 2.5V regulator for U1 and U2.

ON connects to GND to enable the internal LDO regulator for 3.3V mode operation.

SW8

READ_EN,

RD_EN2,

RD_EN3 and

RD_EN4

For manual control of loading the external EEPROM and daisy chain the READ_EN

to the ALL_DONE pins.

Pin1 = ON connects the SW13 push button to the READ_EN of U1.

Pin2,3,4 = OFF

SW9

A_D1 to

RD_EN2 …

A_D3 to

RD_EN4

Pin1 = ON connects the ALL_DONE of U1 to READ_EN of U2.

Pin2 = ON connects the ALL_DONE of U2 to READ_EN of U3.

Pin3 = ON connects the ALL_DONE of U3 to READ_EN of U4.

Pin4 = OFF

SW10

RXDET and

RATE

RXDET – Input internal 50 ohm to VDD terminations

RXDET = F (AUTO RX Detect), RXDET = 1 (50 ohm input termination).

RATE = 0 (GEN1,2) = 2.5G / 5.0G.

RATE = R (GEN3) = 8.0G.

RATE = F (AUTO Detect). The RATE auto detect circuit requires the idle and active

signal which occurs during the link training negotiation.

SW11

EQA[1:0]

PIN MODE – EQ control for channel A inputs