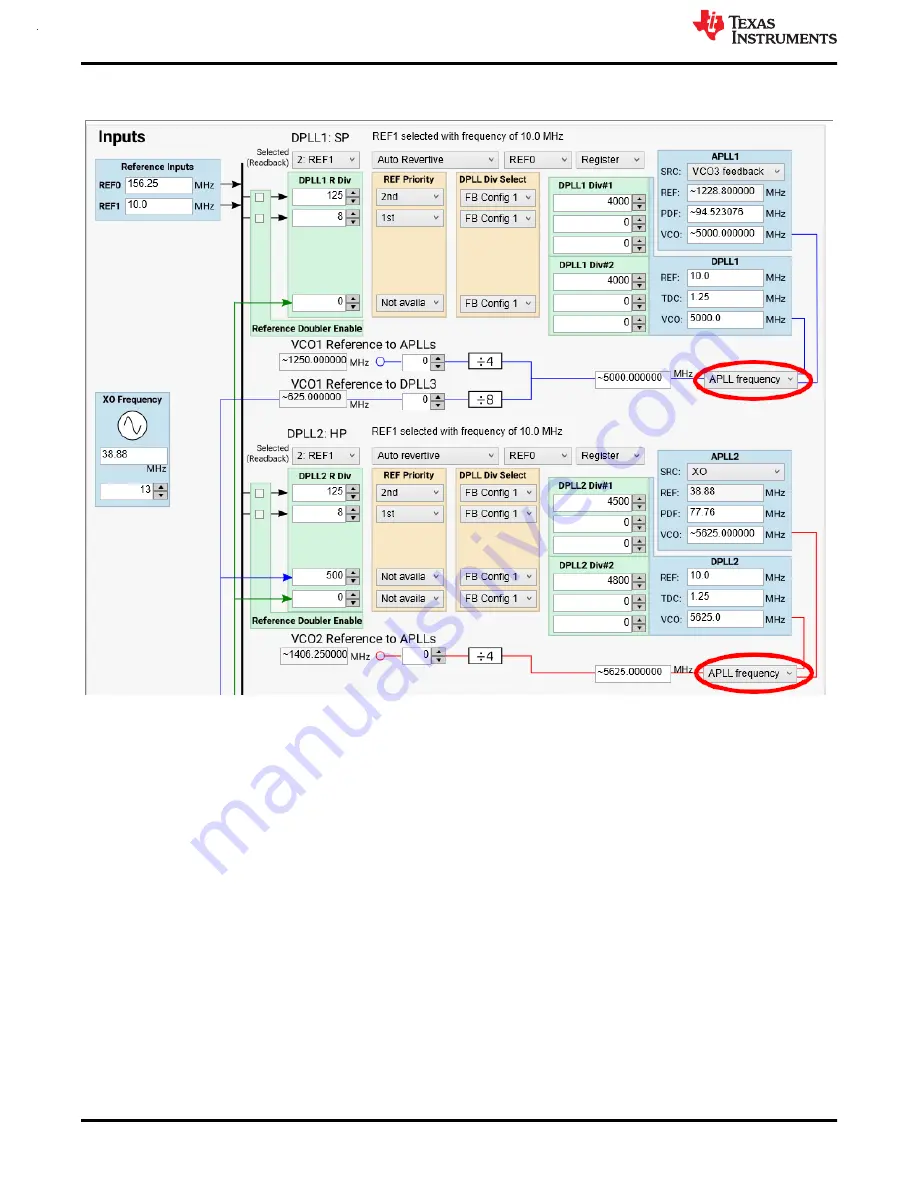

On this page, it is possible to select the APLL frequency or DPLL frequency to propagate through to the outputs

by changing APLL frequency to DPLL frequency.

Figure 6-9. APLL or DPLL Frequency Selection

Appendix A - TICS Pro LMK5C33216 Software

AD

V

A

NCE INFO

R

MA

TION

32

LMK5C33216EVM User's Guide

SNAU260A – OCTOBER 2020 – REVISED FEBRUARY 2021

Copyright © 2021 Texas Instruments Incorporated