I2C Module Registers

1029

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Inter-Integrated Circuit Module

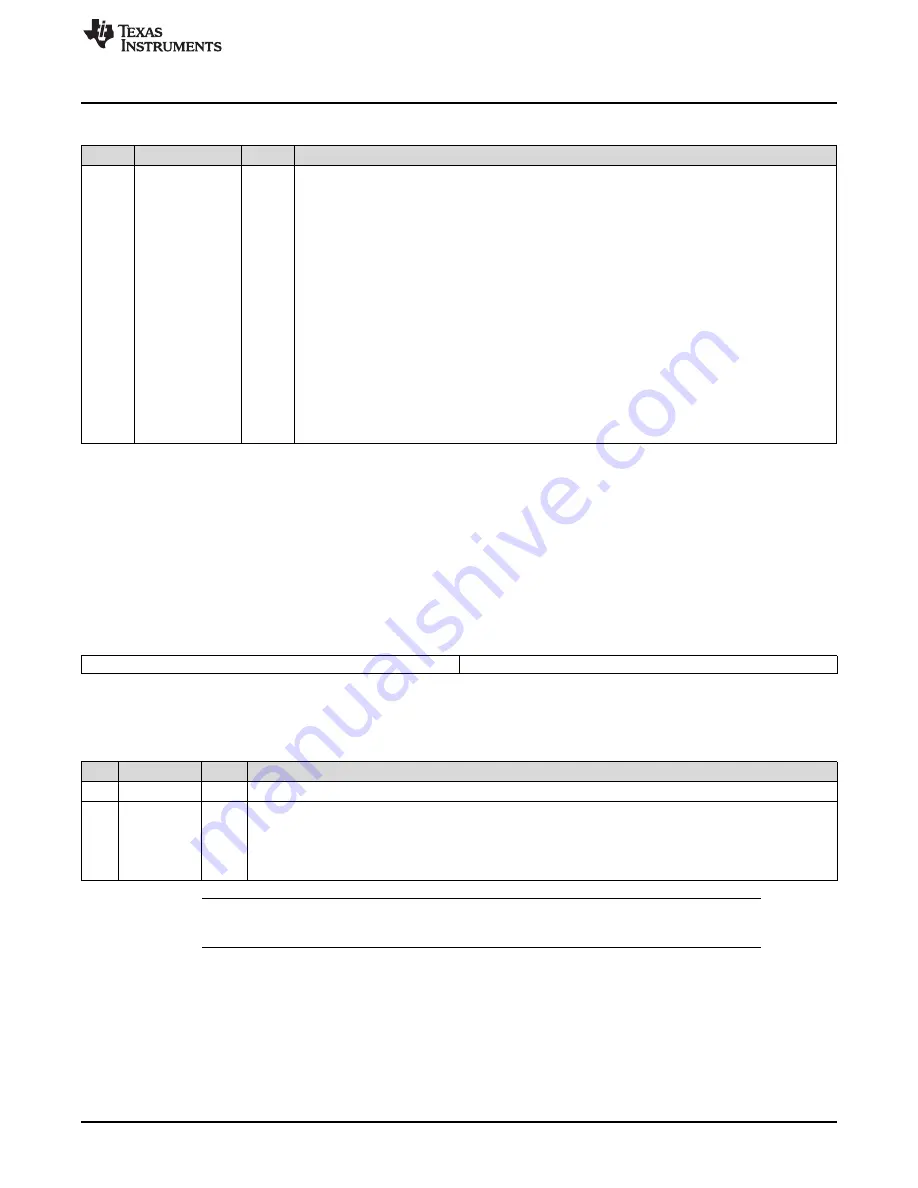

Table 14-11. I2C Interrupt Source Register (I2CISRC) Field Descriptions (continued)

Bit

Field

Value

Description

2-0

INTCODE

Interrupt code bits. The binary code in INTCODE indicates the event that generated an I2C

interrupt.

000

None

001

Arbitration lost

010

No-acknowledgment condition detected

011

Registers ready to be accessed

100

Receive data ready

101

Transmit data ready

110

Stop condition detected

111

Addressed as slave

A CPU read will clear this field. If another lower priority interrupt is pending and enabled, the value

corresponding to that interrupt will then be loaded. Otherwise, the value will stay cleared.

In the case of an arbitration lost, a no-acknowledgment condition detected, or a stop condition

detected, a CPU read will also clear the associated interrupt flag bit in the I2CSTR register.

Emulator reads will not affect the state of this field or of the status bits in the I2CSTR register.

14.5.6 I2C Prescaler Register (I2CPSC)

The I2C prescaler register (I2CPSC) is a 16-bit register (see

) used for dividing down the I2C

input clock to obtain the desired module clock for the operation of the I2C module. See the device-specific

data manual for the supported range of values for the module clock frequency.

lists the bit

descriptions. For more details about the module clock, see

IPSC must be initialized while the I2C module is in reset (IRS = 0 in I2CMDR). The prescaled frequency

takes effect only when IRS is changed to 1. Changing the IPSC value while IRS = 1 has no effect.

Figure 14-21. I2C Prescaler Register (I2CPSC)

15

8

7

0

Reserved

IPSC

R-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -

n

= value after reset

Table 14-12. I2C Prescaler Register (I2CPSC) Field Descriptions

Bit

Field

Value

Description

15-8

Reserved

These reserved bit locations are always read as zeros. A value written to this field has no effect.

7-0

IPSC

I2C prescaler divide-down value.

IPSC determines how much the CPU clock is divided to create the module clock of the I2C module:

module clock frequency = I2C input clock frequency/(IPSC + 1)

Note: IPSC must be initialized while the I2C module is in reset (IRS = 0 in I2CMDR).

NOTE:

To meet all of the I2C protocol timing specifications, the module clock must be configured

between 7-12 MHz.

14.5.7 I2C Clock Divider Registers (I2CCLKL and I2CCLKH)

As explained in

, when the I2C module is a master, the module clock is divided down for

use as the master clock on the SCL pin. As shown in

, the shape of the master clock

depends on two divide-down values:

•

ICCL in I2CCLKL (summarized by

and

). For each master clock cycle, ICCL

determines the amount of time the signal is low.

•

ICCH in I2CCLKH (summarized by

and

). For each master clock cycle, ICCH