Evaluation Software Details

5.1.1

Volatile RAM Configuration Registers –

The lower half of this area displays the volatile configuration registers shown as bit fields, see the

bq76PL536A or bq76PL536A-Q1 data sheet for details on programming these registers. These registers

display green for logic 0 and orange for logic 1. The two states may be toggled between by left-clicking on

the bit

The STATUS, COV_FAULT, and CUV_FAULT bits are either white (logic 0) or red (logic 1) for asserted.

In most cases, the asserted state indicates an error condition sensed by the bq76PL536A.

To clear a fault, first remove the physical condition causing the fault, then click on the ALERT or FAULT

bit to reset the state of the bit. This writes a 1 to the bit, followed by a 0, which is the device’s method for

clearing the asserted bit state back to logic 0.

5.1.2

Group-3 Protected Registers –

The device is provided with many configuration options set by bits contained in a special set of registers

protected against accidental writing. These RAM registers are initialized from OTP (One-Time

Programmable) EPROM cells. The device is shipped with these EPROM locations un-programmed

(blank). The Windows GUI interface hides the un-programmed nature of the device by setting defaults in

the registers cells when the Evaluation software starts (this can be defeated by setting the TOOLS |

OPTIONS defaults). The last settings are also automatically saved by the GUI and restored upon next

use. These features are provided for ease of use and are implemented solely in the GUI. Users are

responsible for programming OTP bits in parts correctly during manufacturing for correct operation in-

circuit.

Some Group-3 registers are shown as registers at the bottom of the left side of the screen, the others in

the top right section of the screen as listboxes and registers

5.1.3

Quick Access

The Quick Access register(s) provide R/W access to any location in the part. They are named arbitrarily in

the GUI ‘X’, ‘Y’, and ‘Z’ – there are no XYZ registers in the part. Some registers, such as the MASTER

register require multi-byte writes to “unlock” the target register for writing. To accomplish this, program the

X register address/data with the first unlock key, the Y register with the second unlock key, and finally the

Z register with the target address and data. Then use the “write all” button to send all three address/data

bytes in the correct order and timing to accomplish the multi-byte write. (This is done automatically when

using the

window.)

5.1.4

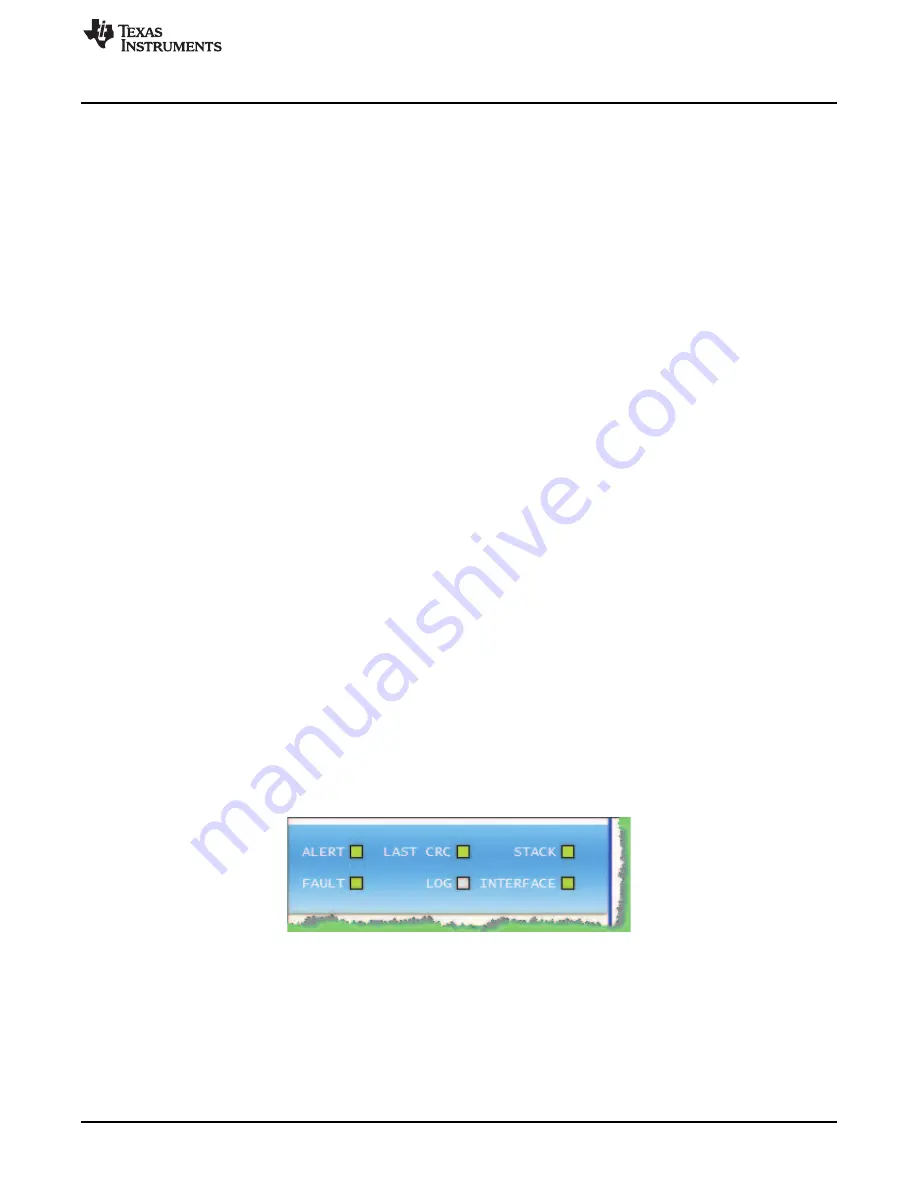

LED Status Indicators

At the top right of the user interface screen are 8 status indicator "LED's". These provide a quick view of

the status of the devices, and the interface, cable connections, etc. Green normally indicates a logic 0

condition, and red a logic one condition. Gray indicates undefined.

ALERT

A condition has been sensed that is causing the ALERT hardware pin to be asserted. This

is also indicated by the ALERT bit being set (red) in the [DEVICE] STATUS register. The

source of the ALERT condition is indicated in the ALERT register just below the STATUS

register.

FAULT

Similar to the ALERT indicator, this LED indicates the FAULT bit, and FAULT hardware

pin are asserted. The source is indicated in the FAULT register just below the ALERT

register.

9

SLUU437D – October 2010 – Revised July 2015

bq76PL536A and bq76PL536A-Q1 EVM Quick Start Guide

Copyright © 2010–2015, Texas Instruments Incorporated