VBUS

GND

VBUS: 3.9V to 6.5V

J1

1

2

3

4

5

6

7

8

J7

VBUS

D+_PSEL

JP3

D-_/PG

JP6

30.1k

R14

10K

TS

10.0k

R15

5.23k

R12

JP5

REGN

JP7

REGN

RTOP TS

4

1

2

3

J6

SCL_OTG

SDA_GND

CD_/CE

10k ohm

R5

383

R3

1.00k

R4

TP8

TP7

TP9

TP10

TP13

TP12

VBUS_IC

PMID

SDA_GND

TP15

TP14

SNS_SYS

BAT

TP11

REGN

MID_/PG

/INT_VSET

SCL_OTG

TP16

TP17

TS

TP18

TP19

D-_/PG

TP20

TP21

D+_PSEL

TP22

CD_/CE

TP23

TP24

TP25

TP26

STAT

TP27

CBSET_ICHGSET

ILIM

10.0k

R10

10.0k

R11

PULL-UP

10.0k

R13

1.02k

R17

PULL-UP

Green

D4

STAT

JP10

1.02k

R18

Green

D5

/PG_LED

SYSTEM

GND

BAT

ISYS+IBAT: up to 2A

J5

BAT

SNS_SYS

TP3

TP4

TP5

TP6

J2

1

2

JP1

PULL-UP

BAT

SYS

LDO_IN

10

R8

20V

D1

40V

D2

0.047uF

C9

REGN

4.7uF

C14

0

R7

110pF

C13

20V

D3

0.01uF

C10

10uF

C11

22uF

C4

0.01uF

C2

22uF

C3

0.01uF

C8

10uF

C7

2

3

JP4

10.0k

R16

REGN

D+_PSEL

PSEL

GND

REGN

PMID

GND

J3

0.01uF

C1

0.01

R1

TP1

TP2

D-

10

8

7

VSET

NC

GND

CE

2

9

D+

VBUS

PMID

PMID

19

20

SW

SW

15

16

13

14

BTST

REGN

25

BQ25886RGER

U1

STAT

TS

ILIM

CD_/CE

SDA_GND

SCL_OTG

D+_PSEL

D-_/PG

/INT_VSET

SW

SW

10.0k

R9

GND

1uH

L1

22uF

C5

22uF

C12

10uF

C6

IBUS: up to 3A

VSYS: up to 8.6V

VBAT: up to 8.4V

VBUS

VBUS_IC

PMID

1uH

L2

JP9

CD_/CE

GND

10k ohm

R19

NT1

Net-Tie

1uF

C15

20V

D6

20V

D7

JP14

JP15

0.01

R2

0.01

R6

2.2uF

C17

1uF

C16

TLV70433DBVT

GND

3

IN

NC

5

U2

SNS_SYS

CD_/CE

82

R20

82

R21

82

R22

82

R23

82

R24

18.0k

R29

39.2k

R26

75.0k

R27

JP16

JP17

JP18

JP19

/INT_VSET

150k

R28

TOP-/BOT+

MID_/PG

MID_/PG

10k ohm

R31

51k

R32

270

R30

MID_/PG

CBSET_ICHGSET

CBSET_ICHGSET

D-_/PG

SCL_OTG

JP8

OTG

GND

JP13

JP2

TP29

TP28

TS

TS

J4

JP12

1

2

3

JP11

MID_/PG

8.2V

8.8V

8.7V

8.4V

82

R25

0.1uF

C18

TP30

SW

0

R33

300

R34

0.01uF

C19

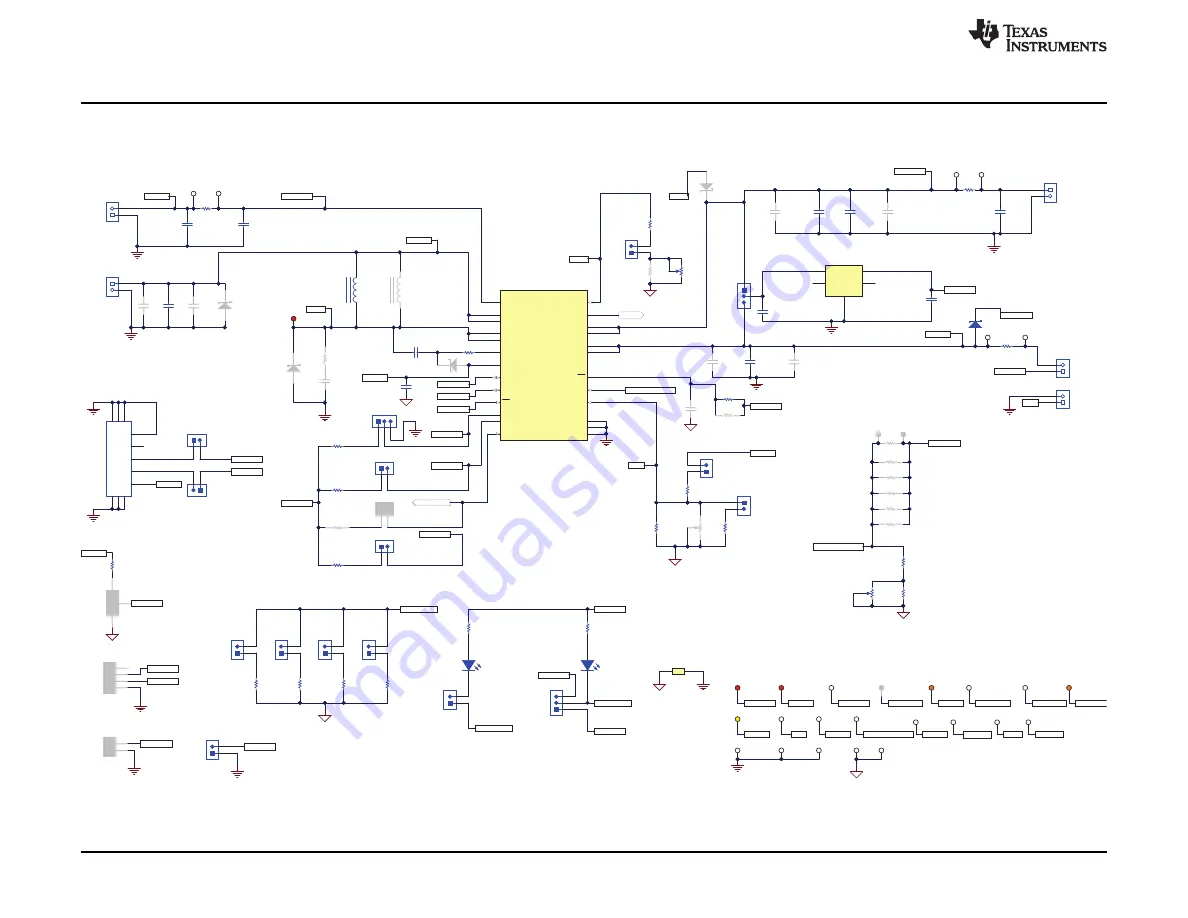

Board Layout, Schematic, and Bill of Materials

12

SLUUC11 – February 2019

Copyright © 2019, Texas Instruments Incorporated

BQ25886 QFN Standalone boost-mode battery charger evaluation module

Advance Information

4.2

Schematic

shows the schematic for the BQ2588x QFN EVM.

Figure 9. BQ25886EVM Schematic