Application Note P4097

© TeraTron GmbH

Page 16 of 21

V1.1, 07.06.01

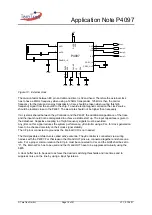

The figure above shows how to enter the value “1” into the serial interface. IN has to be high at least t

S

before the rising edge of CLK. The value for t

S

is given in the datasheet. If this time is chosen to small

or even negative (CLK before IN) the data might not be accepted or the serial interface reset could be

activated. The relative position of the falling edges is uncritical.

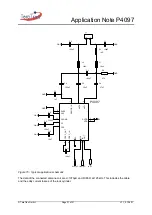

The interface reset with which every serial communication starts is done as defined in the specification

when a rising edge on IN happens while CLK is high.

tres

CLK

ts

Int_Res

IN

Figure 9.: Interface reset

It is recommended that the rising edge on IN appears at least a settle time of t

s

after the rising edge of

CLK. The internal reset is active as long as both signal are high. This time should exceed the

minimum t

res

given in the datasheet. The falling edges of both signals are uncritical, it can have any

order.

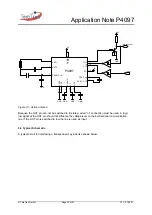

It is necessary to start each writing to the serial shift register with a interface reset. By mistake the

P4097 shift register and the connected µController could not be in phase due to EMI or ESD influence.

In this case the written or read information would be wrong and it is difficult for the µController to figure

this out. For that reason the P4097 is designed to be synchronized at each serial transmission with the

interface reset.

.

Data 1

.

Reset

.

CLK

Reset

Clock 1

Clock 2

IN

Figure 10.: Start of communication

A valid serial command to power up the chip is shown below. It starts with a interface reset to bring the

IC in the command state. Because the IN pin has to be low to achieve this a momentary modulation of

the antenna driver can not be avoided.

The In pin should be pulled high between the 9

th

and the 12

th

clock pulse to avoid modulation at the

end of data transmission.

The pause between the first 8 bits which are input for the chip and the last 3 bits which are the output

should be made longer as shown as due to the analog settle time the outputted data might be wrong.