channel 2 input. The SFP+ module receives the 10G electrical and sends it to the BCM8727 PHY.

The PHY then converts the 10G signal into four 3.125G XAUI output signals and transmits them on

channel 2 to the Stratix IV GX device through the HSMC connector. The same process is followed

for the channel 2 transmitter to channel 1 receiver.

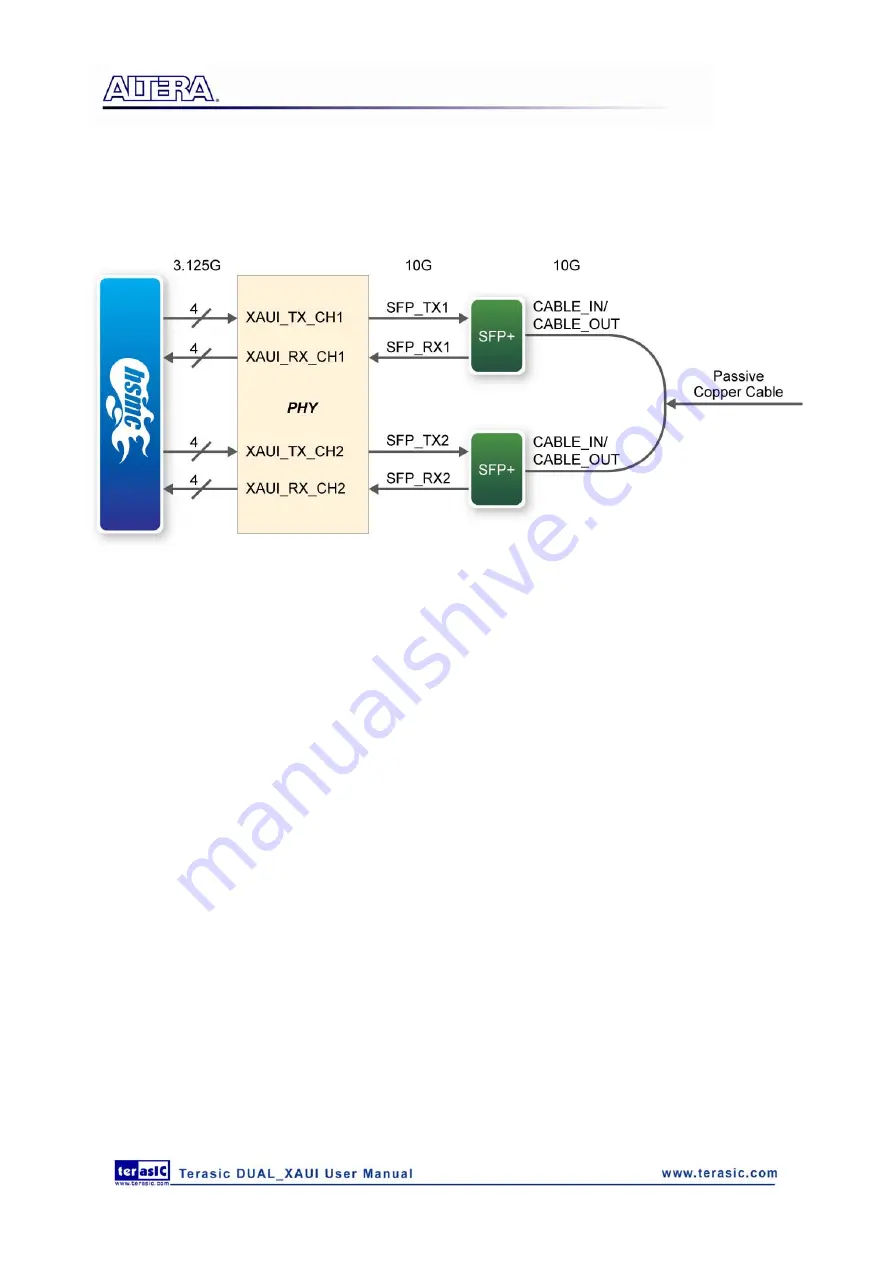

Figure 5-3 XAUI to SFP+ Channel-to-Channel Electrical Loopback Test Setup

XAUI to SFP+ Module 10G Channel-to-Channel Electrical Loopback Test Design Procedure

(The same steps are followed for the Channel Loopback test above, except Step 20 from above is

removed. The reason

this is that the electrical cable unplugs for transmit and receive at the same time.)

1) Set USER_DIPSW[7:0] = [00000100] -- Flip XAUI Lanes

2) Plug in the Dual XAUI to SFP+ HSMC into the HSMA port on the Stratix IV GX FPGA

development

3) Plug in SFP+ modules into each SFP+ port on the Dual XAUI to SFP+ HSMC

4) Power on the Stratix IV GX FPGA development kit board

5) Program the Stratix IV GX FPGA development kit with the "hsmc_loopback.sof"

On the Stratix IV GX FPGA development kit:

7) Press and release cpu_resetn (S2).

8) Press and release user_pb[0] -- the rx is now ready to search for a prbs seed pattern

9) Press and release both cpu_resetn, user_pb[1] and user_pb[2] simultaneously

- Resets the BCM8727C device and the + SFP module(s)

10) Reset Module (It should be OK to skip this one, but include these steps if your board is failing)

A) Set USER_DIPSW[7:0] = [00000000] (Program MDIO to reset module)

B) Press and release user_pb[1]

32