Advance Information

UM-TM57PA20&40_E

8 Bit Microcontroller

6

tenx technology, inc.

Preliminary

Rev 1.3, 2009/10/19

FUNCTIONAL DESCRIPTION

1. CPU Core

1.1 Clock Scheme and Instruction Cycle

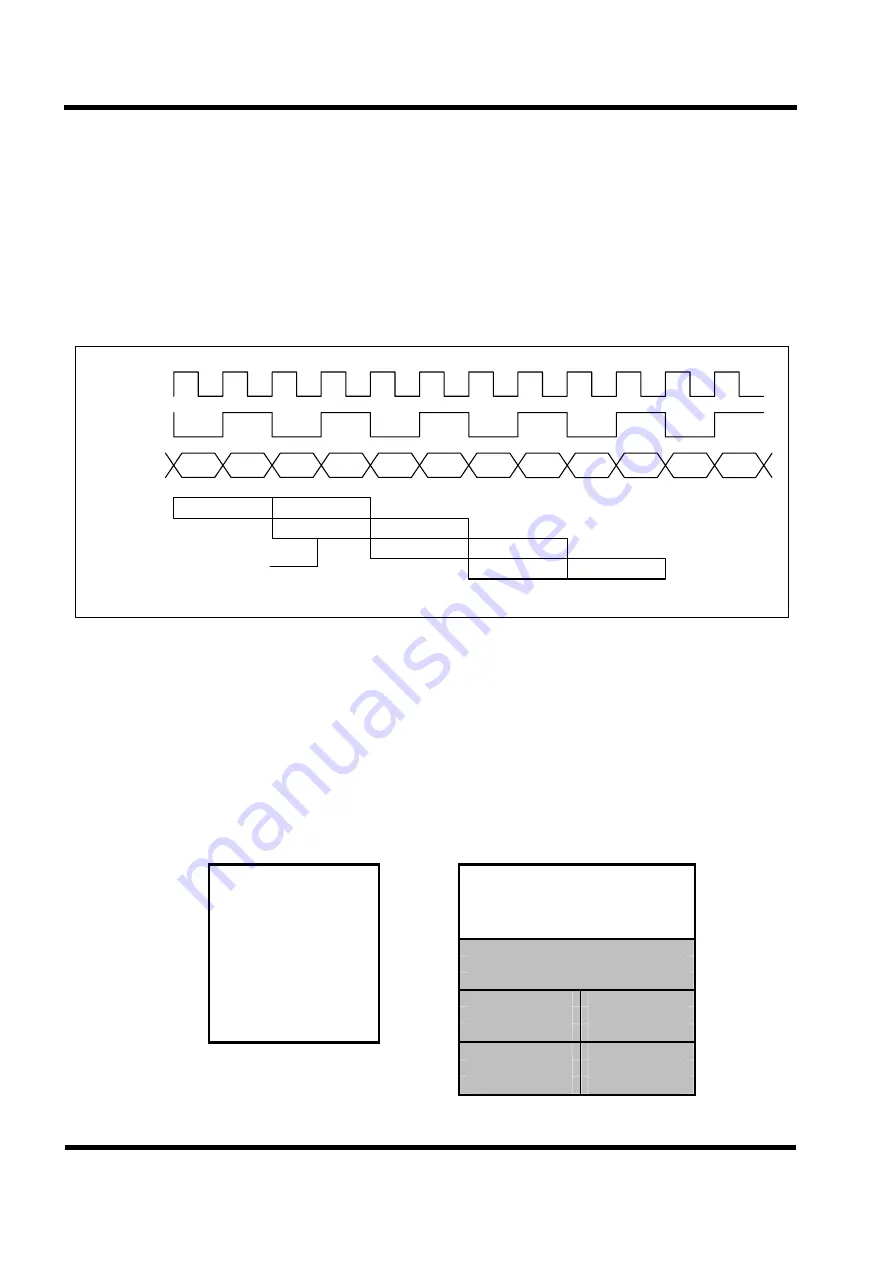

The system clock is internally divided by two to generate Q1 state and Q2 state for each instruction

cycle. The Programming Counter (PC) is updated at Q1 and the instruction is fetched from program

ROM and latched into the instruction register in Q2. It is then decoded and executed during the

following Q1-Q2 cycle. Branch instructions take two cycles since the fetch instruction is ‘flushed’ from

the pipeline, while the new instruction is being fetched and then executed.

Fetch

Execute

Branch

Instruction

Instruction

Pipeline

Flow

Fetch

Execute

Fetch

Flush

Fetch

Execute

Instruction

Cycle

F

OSC

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

Q1

Q2

1.2 Addressing Mode

There are two Data Memory Planes in CPU, R-Plane and F-Plane. The registers in R-Plane are write-

only. The “MOVWR” instruction copy the W-register’s content to R-Plane registers by direct addressing

mode.

The lower locations of F-Plane are reserved for the SFR. Above the SFR is General Purpose Data

Memory, implemented as static RAM. F-Plane can be addressed directly or indirectly. Indirect

Addressing is made by INDF register. The INDF register is not a physical register. Addressing INDF

actually addresses the register whose address is contained in the FSR register (FSR is a pointer). The

first half of F-Plane is bit-addressable, while the second half of F-Plane is not bit-addressable.

R-Plane

F-Plane

00

00

SFR

Bit

Addressable

MOVWR

Instruction

1F

Write

Only 20

RAM

Bit Addressable

27

28

RAMBANK=0

RAMBANK=1

Bit Addressable

Bit Addressable

3F

3F

40

RAMBANK=0

RAMBANK=1

7F