17-2000 C

2020-09-17

6(50)

ADQ8-8C Manual

17-2000 C 2020-09-17

6(50)

The number representation is 2’s complement. The full scale maximum code is then 32 704 and the full

scale minimum code is –32 768. Overflow or underflow at any position in the signal path will saturate

the data and turn on an overflow flag. See

for more information on over- and under-flow.

1.2.2

Calibration

During the factory calibration procedure the analog properties are measured and parameters for a digi-

tal compensation are computed. An analog deviation in the front-end is thus compensated for by the

inverse function in the digital signal processing part.

Example 1: With the variable gain –VG option (always included with the ADQ8-8C), the user requests

a range. The closest available setting is selected and the actual range is returned to the user for being

used in the user’s algorithms, see

Example 2: The full scale signal range of the ADQ is measured in production and the

SetGainAndOff-

set

function is used for adjusting to the correct signal range.

1.2.3

Data acquisition nomenclature

defines some key data acquisition terms.

1.2.4

Sampling clock frequency

The ADQ8-8C is designed for the specified 1 GHz clock frequency only. A different sampling rate can

be achieved by using the sample skip function,

.

1.2.5

System clocks

The different parts of the digitizer operate on different clock rates

The sampling of the analog signal is done on the sampling clock of the ADC (see

).

The external trigger input has a trigger clock which is higher than the sample clock for high trigger time

precision (4 GHz).

The PCIe host PC connections has its own clock system.

All other interfaces operate on the data processing clock of the FPGA at 250 MHz. This clock is referred

to as the Data Clock.

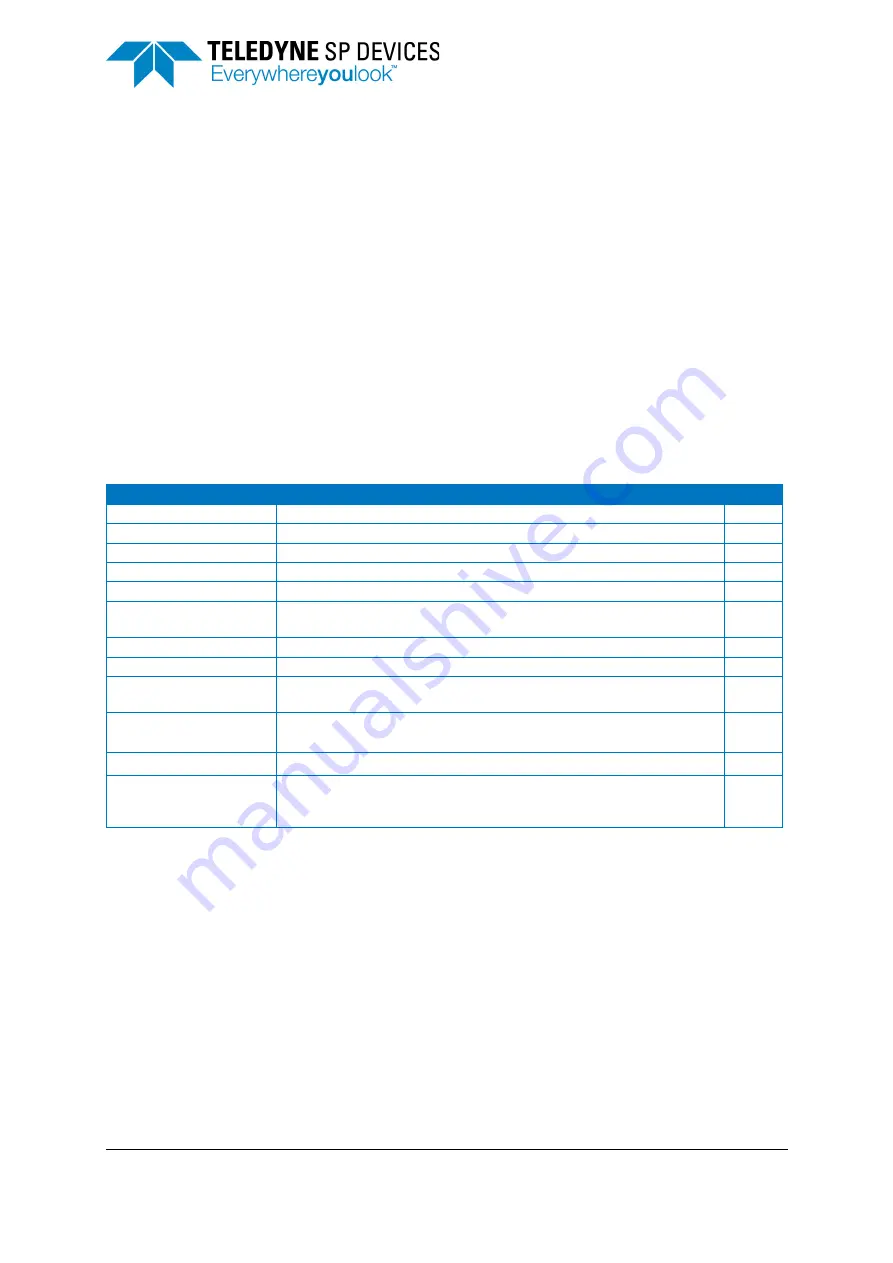

Table 1: Data recording nomenclature.

PARAMETER

DESCRIPTION

REF

ADQ

Collective name for digitizers from Teledyne SP Devices.

Analog

Analog signal is the input to the digitizer. This is the signal to be digitized.

Waveform

Analog signal with a distribution in time. This is digitized into a record.

Sample

An analog signal level is digitized into a sample, that is a numerical value.

SYNC

Physical connector on the front panel.

Record

A set of consecutive samples is called a record. An analog waveform is

digitized into a record of samples.

TRIG

Physical connector on the front panel.

Trigger

Trigger is an event that starts acquisition of a record.

Timestamp

Timestamp is a real-time value that identifies when a trigger happened.

The timestamp gives timing information for each sample.

GSPS

Giga-samples per second (10

9

). Clock frequency [Hz] and sample rate

[SPS] are both used to denote speed.

MSPS

Mega-sample per second (10

6

).

DC-offset

This is an analog DC level which is added to the analog input signal inside

the digitizer to vertically move the analog signal to fit within the range of

the digitizer. This effectively doubles the ENOB for a unipolar signal.