13

PIN No.

SYMBOL

I/O

DESCRIPTION

70

72 ~ 79

82

83

84

85

86

87

88

89

92 ~ 99

RAMA2

RAMD0~7

SDWCK0

SDBCK0

SDIA0

SDIA1

RAMA1

RAMA0

RAMWEN

RAMOEN

IPORT7~0

O

I+/O

I

I

I

I

O

O

O

O

I+

External SRAM interface address 2

External SRAM interface data (STREAM0~7 output when External SRAM is not in use)

Word clock input for SDIA, SDOA, SDIB, SDOB

Bit clock input for SDIA,SDOA,SDIB,SDOB

AC-3 Bitstream (or PCM) data input for Main DSP

AC-3 Bitstream (or PCM) data input for Main DSP

External SRAM interface address 1

External SRAM interface address 0

External SRAM interface /WE

External SRAM interface /OE

Input port for general purpose (not use)

NOTE)

Is: Schmidt trigger input terminal

It: Input terminal with pull-up resistor

O: Digital output terminal

Ot: Tri-state digital output terminal

A: Analog terminal

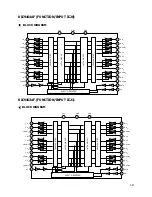

100 99 98 97 96 95 94 93 92 91 90 89 88 87 86 85 84 83 82 81

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

80

79

78

77

76

75

74

73

72

71

70

68

67

66

65

64

63

62

61

60

69

58

57

56

55

54

53

52

51

59

1

VDD1

V

SS

IPOR

T0

IPOR

T1

IPOR

T2

IPOR

T3

IPOR

T4

IPOR

T5

IPOR

T6

IPOR

T7

VDD2

VSS

RAMOEN

RAMWEN

RAMA0

RAMA1

SDIA1

SDIA0

SDBCK0

SDWCK0

VDD2

VDD1

OPOR

T0

OPOR

T1

OPOR

T2

OPOR

T3

OPOR

T4

OPOR

T5

OPOR

T6

OPOR

T7

VDD2

VSS

RAMA9

RAMA8

RAMA7

SDOB2

SDOB1

SDOB0

SDBCK1

SDWCK1

VSS

RAMCEN

RAMA16

RAMA15

SDIB0

SDIB1

SDIB2

XI

XO

VSS

AVDD

SDIB3

TEST

TEST

OVFB

DTSDATA

AC3DATA

SDOB3

CPO

AVSS

VDD2

SDOA2

SDOA1

SDOA0

RAMA14

RAMA13

RAMA12

RAMA11

RAMA10

VSS

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

21

12

23

24

25

26

27

28

29

30

22

VSS

RAMD7

RAMD6

RAMD5

RAMD4

RAMD3

RAMD2

RAMD1

RAMD0

VDD1

RAMA2

SCK

SI

SO

/CS

/CSB

RAMA3

TEST

/IC

RAMA4

VSS

RAMA5

RAMA6

/SDBCK0

SURENC

KARAOKE

MUTE

CRC

NONPCM

VDD2

YSS912C PIN CONFIGURATION