Advanced-control timers (TIM1&TIM8)

RM0090

532/1731

DocID018909 Rev 11

17.3.7

PWM input mode

This mode is a particular case of input capture mode. The procedure is the same except:

•

Two ICx signals are mapped on the same TIx input.

•

These 2 ICx signals are active on edges with opposite polarity.

•

One of the two TIxFP signals is selected as trigger input and the slave mode controller

is configured in reset mode.

For example, you can measure the period (in TIMx_CCR1 register) and the duty cycle (in

TIMx_CCR2 register) of the PWM applied on TI1 using the following procedure (depending

on CK_INT frequency and prescaler value):

•

Select the active input for TIMx_CCR1: write the CC1S bits to 01 in the TIMx_CCMR1

register (TI1 selected).

•

Select the active polarity for TI1FP1 (used both for capture in TIMx_CCR1 and counter

clear): write the CC1P and CC1NP bits to ‘0’ (active on rising edge).

•

Select the active input for TIMx_CCR2: write the CC2S bits to 10 in the TIMx_CCMR1

register (TI1 selected).

•

Select the active polarity for TI1FP2 (used for capture in TIMx_CCR2): write the CC2P

and CC2NP bits to ‘1’ (active on falling edge).

•

Select the valid trigger input: write the TS bits to 101 in the TIMx_SMCR register

(TI1FP1 selected).

•

Configure the slave mode controller in reset mode: write the SMS bits to 100 in the

TIMx_SMCR register.

•

Enable the captures: write the CC1E and CC2E bits to ‘1’ in the TIMx_CCER register.

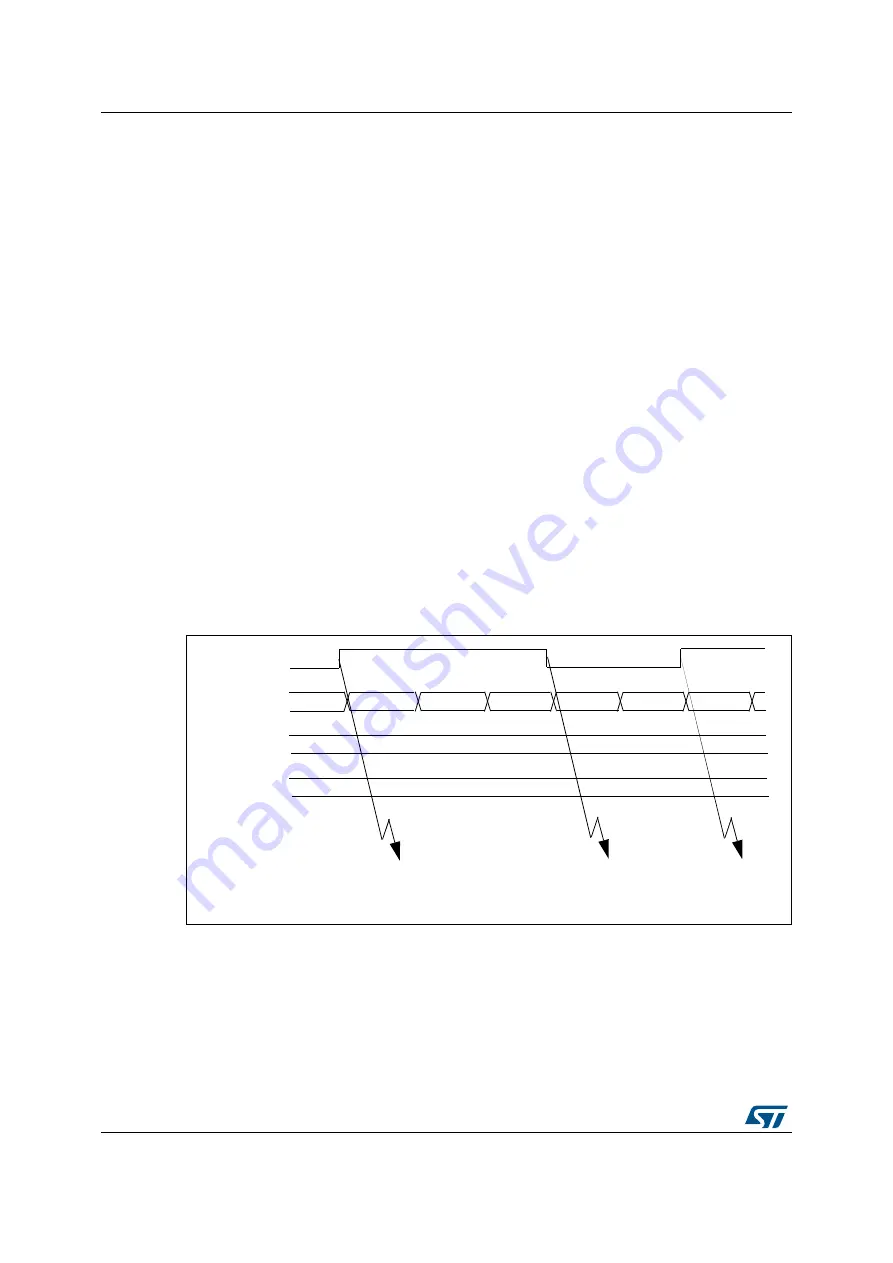

Figure 116. PWM input mode timing

TI1

TIMx_CNT

0000

0001

0002

0003

0004

0000

0004

TIMx_CCR1

TIMx_CCR2

0004

0002

IC1 capture

IC2 capture

reset counter

IC2 capture

pulse width

IC1 capture

period

measurement

measurement

ai15413