System overview

UM0874

14/33

Doc ID 16844 Rev 1

4 System

overview

4.1

Hardware design description

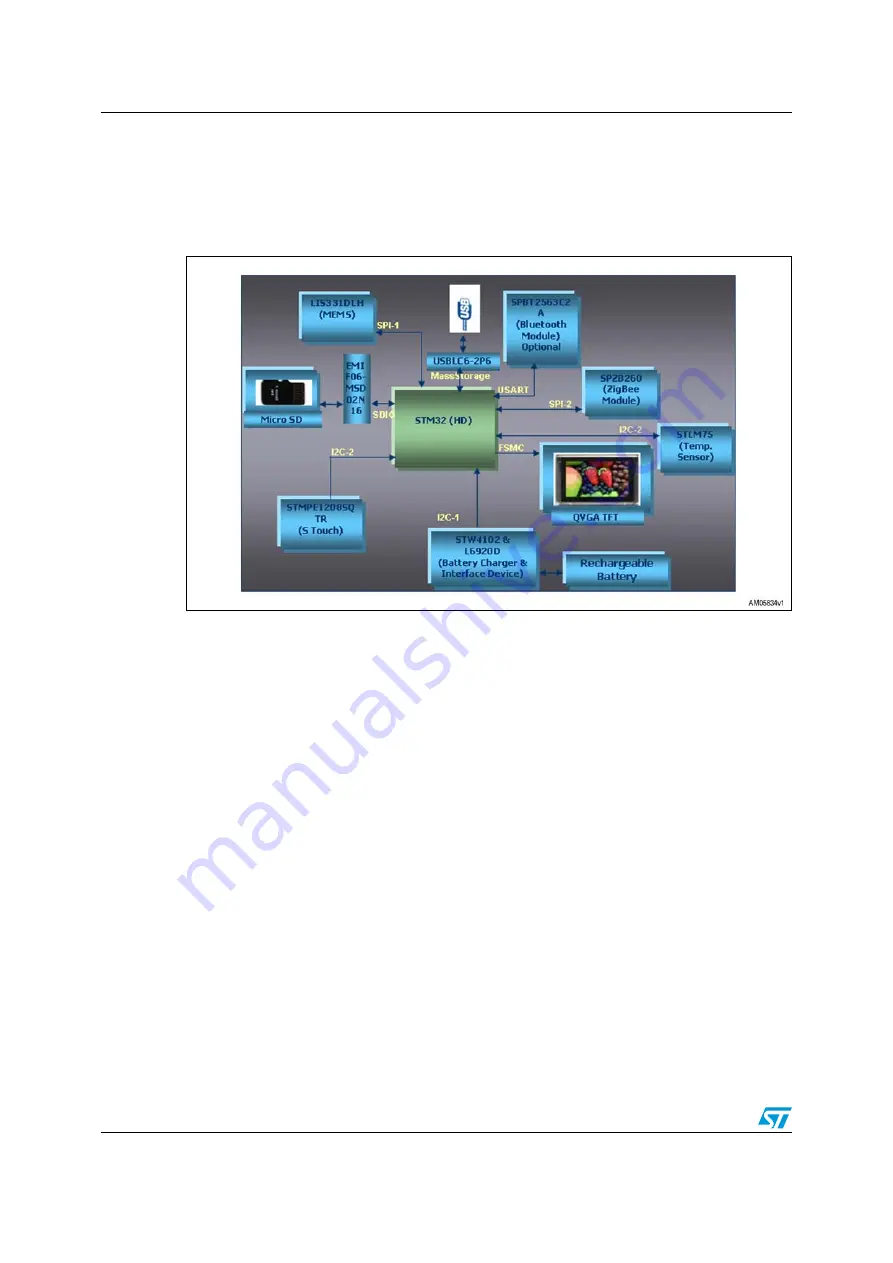

Figure 16.

System block diagram

The hardware block diagram is given in

. As shown, the STM32 microcontroller is

the main controller of the system.

4.1.1 Microcontroller

(STM32)

The STM32 is a 32-bit MCU based on the popular ARM 32-bit Cortex™-M3 CPU running at

72 MHz with performance of 90 DMIPS with 1.25 DMIPS/MHz. The memories embedded in

it contain up to 20 Kbytes of SRAM and 128 Kbytes of flash memory. The microcontroller

has single-cycle multiplication and hardware division. It has 80 fast general-purpose IOs to

enhance the overall performance. The IOs are 5 V tolerant.

The microcontroller has up to 9 communication interfaces which include two I

2

Cs

(400 kHz), three USARTs (4.5 Mbps), two SPIs (18 MHz), CAN 2.0B active interface and

USB 2.0 (12 Mbps) full-speed interface. For more details, please refer to the STM32F103VE

datasheet.

For the digital photo frame application, the firmware is using the two SPIs, two I

2

Cs, SDIO,

FSMC and USB interfaces. One of the SPIs is interfaced with MEMS and the other one with

the ZigBee

®

module. The SD card is interfaced with SDIO and the TFT with FSMC. The

STLM75 and STMPE1208SQTR use I

2

C-2 and the STW4102 uses I

2

C-1 to communicate

with the controller.

The microcontroller works on a single voltage from 2 V to 3.6 V, unlike several

microcontrollers requiring dual voltage. In this application the voltage bus is managed with

3.3 V.

www.BDTIC.com/ST