Synchronization (Option)

The setup order for the different synchronization options

(c) Spectrum GmbH

85

When the boards are synchronized by the option starhub there

will be no delay between the connected boards. This is achie-

ved as all boards, including the one the starhub module is

mounted on, are connected to the starhub with cables of the

same length.

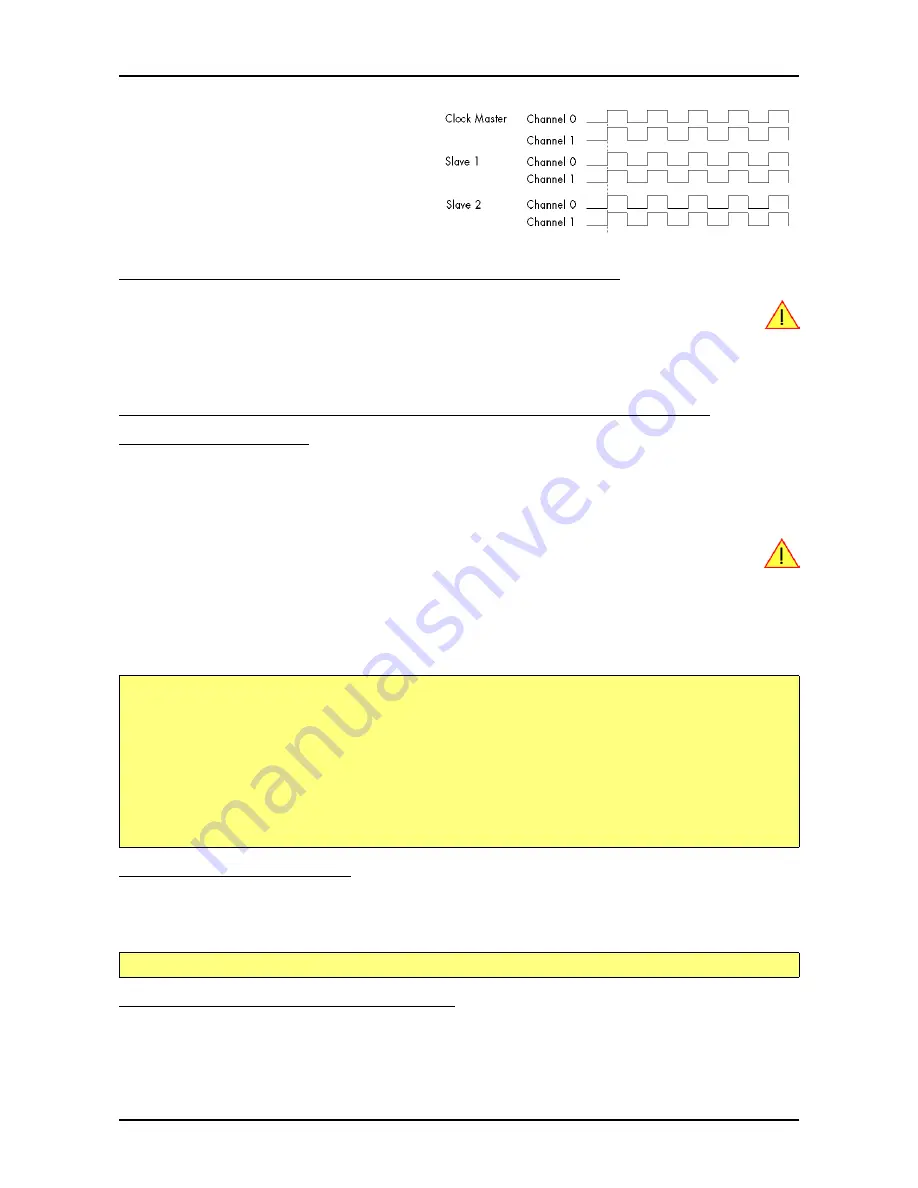

The figure on the right shows the clock of three boards with two

channels each that are synchronized by starhub.

The setup order for the different synchronization options

If you setup the boards for the use with synchronization it is important to keep the order within the software

commands as mentioned below to get the boards working correctly.

Depending on if you use the board either in standard or in FIFO mode there are slightly different orders in the setup for the synchronization

option. The following steps are showing the setups either for standard or FIFO mode.

Setup Order for use with standard (non FIFO) mode and equally clocked boards

(1) Set up the board parameters

Set all parameters like for example sample rate, memsize and trigger modes for all the synchronized boards, except the dedicated registers

for the synchronization itself that are shown in the tables below.

All boards must be set to the same settings for the entire clocking registers (see the according chapter for sample rate generation), for the

trigger mode and memory and should be set to the same postcounter size to get the same pretrigger sizes as well.

If you use acquisition boards with different pretrigger sizes, please keep in mind that after starting the board

the pretrigger memory of all boards will be recorded first, before the boards trigger detection is armed. Take

care to prevent boards with a long pretrigger setup time from hangup by adequately checking the board’s

status. Long setup times are needed if either you use a huge pretrigger size and/or a slow sample rate.

If you don’t care it might happen that boards with a small pretrigger are armed first and detect a triggerevent, while one or more boards with

a huge pretrigger are still not armed. This might lead to an endless waiting-state on these boards, which should be avoided.

Example of board setup for three boards

(2) Let the master calculate it’s clocking

To obtain proper clock initailization when doing the first start it is necessary to let the clock master do all clock related calculations prior to

setting all the synchronization configuration for the slave boards.

Example of board #0 set as clock master and forced to do the appropriate clock calculation

(3) Write Data to on-board memory (output boards only)

If one or more of the synchronized boards are used for generating data (arbitrary waveform generator boards or digital I/O boards with

one or more channels set to output direction) you have to transfer the data to the board’s on-board memory before starting the synchronization.

Please refer to the related chapter for the standard mode in this manual. If none of your synchronized boards is used for generation purposes

you can ignore this step.

// --------- Set the Handles to fit for Windows driver ---------

hDrv[0] = 0;

hDrv[1] = 1;

hDrv[2] = 2;

// (1) ----- Setup all boards, shortened here !!!-----

for (i = 0; i < 3; i++)

{

SpcSetParam (hDrv[i], SPC_MEMSIZE, 1024); // memory in samples per channel

SpcSetParam (hDrv[i], SPC_POSTTRIGGER, 512); // posttrigger in samples

// ...

SpcSetParam (hDrv[i], SPC_SAMPLERATE, 10000000); // set sample rate to all boards

SpcSetParam (hDrv[i], SPC_TRIGGERMODE, TM_SOFTWARE); // set trigger mode to all boards

}

SpcSetParam (hDrv[0], SPC_COMMAND, SPC_SYNCCALCMASTER); // Calculate clock settings on master