1-13

IC

VGN-

S36C/S36GP/S36LP/S36SP/S36TP/S38CP/

S52B/

S62PS/S62PSY/S62S/

S350F/S350FP/

S360/S360P/

S370F

(J/AM

/AO

)

Confidential

AC CHARACTERISTICS - I (continue)

Parameter

Symbol

28

33

36

Unit

Note

Min

Max

Min

Max

Min

Max

Row Cycle Time

t

RC

16

-

14

-

14

-

CK

Auto Refresh Row Cycle Time

t

RFC

17

-

17

-

16

-

CK

Row Active Time

t

RAS

10

120K

9

120K

9

120K

CK

Row Address to Column Address Delay for Read

t

RCDRD

5

-

5

-

5

-

CK

Row Address to Column Address Delay for Write

t

RCDWR

2

-

2

-

2

-

CK

Row Active to Row Active Delay

t

RRD

4

-

3

-

3

-

CK

Column Address to Column Address Delay

t

CCD

1

-

1

-

1

-

CK

Row Precharge Time

t

RP

5

-

5

-

5

-

CK

Write Recovery Time

t

WR

3

-

3

-

3

-

CK

Last Data-In to Read Command

t

DRL

2

-

2

-

2

-

CK

Auto Precharge Write Re Precharge Time

t

DAL

8

-

8

-

8

-

CK

System Clock Cycle Time

CL=5

t

CK

2.8

6

-

-

-

-

ns

CL=4

-

-

3.3

10

3.6

10

ns

CL=3

-

-

4.5

10

4.5

10

ns

Clock High Level Width

t

CH

0.45

0.55

0.45

0.55

0.45

0.55

CK

Clock Low Level Width

t

CL

0.45

0.55

0.45

0.55

0.45

0.55

CK

Data-Out edge to Clock edge Skew

t

AC

-0.6

0.6

-0.6

0.6

-0.6

0.6

ns

DQS-Out edge to Clock edge Skew

t

DQSCK

-0.6

0.6

-0.6

0.6

-0.6

0.6

ns

DQS-Out edge to Data-Out edge Skew

t

DQSQ

-

0.35

-

0.35

-

0.4

ns

Data-Out hold time from DQS

t

QH

tHPmin

-tQHS

-

tHPmin

-tQHS

-

tHPmin

-tQHS

-

ns

1,6

Clock Half Period

t

HP

tCH/L

min

-

tCH/L

min

-

tCH/L

min

-

ns

1,5

Data Hold Skew Factor

t

QHS

-

0.35

-

0.35

-

0.4

ns

6

Input Setup Time

t

IS

0.75

-

0.75

-

0.75

-

ns

2

Input Hold Time

t

IH

0.75

-

0.75

-

0.75

-

ns

2

Write DQS High Level Width

t

DQSH

0.4

0.6

0.4

0.6

0.4

0.6

CK

Write DQS Low Level Width

t

DQSL

0.4

0.6

0.4

0.6

0.4

0.6

CK

Clock to First Rising edge of DQS-In

t

DQSS

0.85

1.15

0.85

1.15

0.85

1.15

CK

Data-In Setup Time to DQS-In (DQ & DM)

t

DS

0.35

-

0.35

-

0.4

-

ns

3

N

ote :

1.

This calculation accounts for tDQSQ(max), the pulse width distortion of on-chip circuit and jitter.

2.

Data sampled at the rising edges of the clock : A0~A11, BA0~BA1, CKE, /CS, /RAS, /CAS, /WE.

3.

Data latched at both rising and falling edges of Data Strobes(DQS0~DQS3) : DQ, DM(0~3).

4.

Minimum of 200 cycles of stable input clocks after Self Refresh Exit command, where CKE is held high, is required to complete

Self Refresh Exit and lock the internal DLL circuit of DDR SDRAM.

5.

Min (tCL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this

value can be greater than the minimum specification limits for tCL and tCH).

6. tHP = minimum half clock period for any given cycle and is defined by clock high or clock low (tCH, tCL).

tQHS consists of tDQSQmax, the pulse width distortion of on-chip clock circuits, data pin to pin skew and

output pattern effects, and p-channel to n-channel variation of the output drivers.

7. DQS, DM and DQ input slew rate is specified to prevent double clocking of data and preserve setup and hold times.

Signal transitions through the DC region must be monotonic.

Data-In Hold Time to DQS-In (DQ & DM)

t

DH

0.35

-

0.35

-

0.4

-

ns

3

Read DQS Preamble Time

t

RPRE

0.9

1.1

0.9

1.1

0.9

1.1

CK

Read DQS Postamble Time

t

RPST

0.4

0.6

0.4

0.6

0.4

0.6

CK

Write DQS Preamble Setup Time

t

WPRES

0

-

0

-

0

-

ns

Write DQS Preamble Hold Time

t

WPREH

0.35

-

0.35

-

0.35

-

CK

Write DQS Postamble Time

t

WPST

0.4

0.6

0.4

0.6

0.4

0.6

CK

Mode Register Set Delay

t

MRD

2

-

2

-

2

-

CK

Exit Self Refresh to Any Execute Command

t

XSC

200

-

200

-

200

-

CK

4

Power Down Exit Time

t

PDEX

2tCK

+ tIS

-

2tCK

+ tIS

-

1tCK

+ tIS

-

CK

Average Periodic Refresh Interval

t

REFI

-

7.8

-

7.8

-

7.8

us

Parameter

Symbol

28

33

36

Unit

Note

Min

Max

Min

Max

Min

Max

AC CHARACTERISTICS - II

Frequency

CL

tRC

tRFC

tRAS

tRCDRD

tRCDWR

tRP

tDAL

Unit

500MHz (2ns)

5

23

26

16

7

4

7

11

tCK

450MHz (2.2ns)

5

21

24

14

7

3

7

11

tCK

400MHz (2.5ns)

5

18

21

12

6

3

6

9

tCK

350MHz (2.8ns)

5

16

17

10

5

2

5

8

tCK

300MHz (3.3ns)

4

14

17

9

5

2

5

8

tCK

275MHz (3.6ns)

4

14

16

9

5

2

5

8

tCK

250MHz (4.0ns)

4

13

15

8

5

2

5

8

tCK

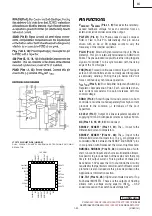

HYB25D128323C-3.3 (INFINEON)

MEMORIES FOR GRAPHICS SYSTEMS

128 BALL XBGA

4 Banks x 4096 Rows

x 256 Columns x 32 Bits

1

2

3

12

10

11

D

B

C

H

E

F

G

M

J

K

L

V

SSQ

A

V

SSQ

9

7

8

6

4

5

DQ

4

DQS

0

DQ

3

DM

0

V

DDQ

DQ

2

DQ

0

DQ

31

DQ

29

DQ

28

DM

3

DQS

3

NC

V

DDQ

DQ

1

V

DDQ

V

DDQ

DQ

30

V

DDQ

NC

V

DDQ

DQ

26

DQ

27

DQ

6

DQ

5

V

SSQ

V

SSQ

V

SSQ

V

DD

V

DD

V

SSQ

V

SSQ

V

SSQ

DQ

24

DQ

25

V

DDQ

V

DD

V

SS

V

SSQ

V

SS

V

SS

V

SSQ

V

SS

V

DD

DQ

7

V

DDQ

DQ

17

DQ

16

V

DDQ

V

SSQ

V

SSQ

DQ

15

V

DDQ

DQ

14

DQ

12

DQ

13

V

DDQ

DQ

11

V

SSQ

DQ

8

V

SSQ

DQ

9

NC

DM

1

DQS

1

DQ

10

V

REF

V

DDQ

V

SSQ

DQ

18

DQ

19

V

DDQ

V

SSQ

V

SSQ

DQ

20

DM

2

NC

DQS

2

DQ

21

DQ

22

V

DDQ

V

SSQ

DQ

23

V

DDQ

V

SSQ

V

SS

V

SS

A

6

V

SSQ

CKE

V

DDQ

NC

CLK

NC

V

DD

A

5

A

9

V

SS

RFU

A

10

V

DD

V

DD

A

2

V

SS

RAS#

WE#

V

DD

CAS#

CS#

BA

1

BA

0

NC

NC

NC

A

1

A

3

A

0

A

11

A

4

RFU

A

7

CLK#

MCL

A8/AP

V

SS

V

SS

TOP VIEW

1.5

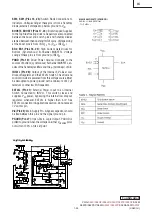

Signal and Pin Description

Note: The “#” sign marks a signal as low active.

Table 2

Signal and Pin Description

Pin

IO Type

Detailed Function

CLK, CLK#

Input

Clock

: CLK and CLK# are differential clock inputs. All address and command inputs are latched on the

crossing of the positive edge of CLK and the negative edge of CLK#. Output data (DQ’s and DQS) is

referenced to the crossing of CLK and CLK#.

CKE

Input

Clock Enable

: CKE HIGH activates and CKE LOW deactivates the internal clock, input buffers and

output drivers. Taking CKE LOW provides PRECHARGE POWER-DOWN and SELF REFRESH

operations (all banks idle), or ACTIVE POWER-DOWN (row active in any bank). CKE is synchronous

for POWER-DOWN entry and exit, and for SELF REFRESH entry. CKE is asynchronous for SELF-

REFRESH exit. CKE must be maintained HIGH trough out READ and WRITE accesses. Input buffers

(excluding CLK, CLK#) are disabled during POWER-DOWN. Input buffers (excluding CKE) are

disabled during SELF REFRESH. CKE is an SSTL2 input but will detect an LVCMOS LOW level after

VDD is applied.

CS#

Input

Chip Select

: CS# enables the command decoder when low and disables it when high. When the

command decoder is disabled, new commands are ignored, but internal operations continue. CS# is

considered part of the command code.

RAS#, CAS#, WE#

Input

Command Inputs

: CAS#, RAS#, and WE# (along with CS#) define the command to be executed.

BA1, BA0

Input

Bank Address Inputs

: BA0 and BA1 select to which internal bank an ACTIVE, READ, WRITE, or

PRECHARGE command is being applied. They also define which mode register (mode register or

extended mode register) is loaded during a MODE REGISTER SET command.

A11.. A0

Input

Address Inputs

: During a Bank Activate command cycle, A0-A11 defines the row address (RA0-

RA11). During a Read or Write command cycle, A0-A7 defines the column address (CA0-CA7).

In addition to the column address, A8/AP is used to invoke autoprecharge operation at the end of the

burst read or write cycle. If A8 is high, the active bank is precharged. If A8 is low, the Autoprecharge

function is disabled.

During a Precharge command cycle, A8/AP is used to determine, which bank(s) will be precharged. If

A8/AP is high, all four banks will be precharged regardless of the state of BA0 and BA1. If A8/AP is low,

BA0 and BA1 define the bank to be precharged.

The address inputs also provide the op-code during a MODE REGISTER SET command.

DQS3.. DQS0

I/O

Data Strobes

: The DQSx are the bidirectional strobe signals. At read cycles, the DQSx signals are

generated by the SGRAM and are edge-aligned to the data. At write cycles, the DQS signals are

generated by the controller. The rising or falling edge indicates the center of the data valid window.

Before and after a transfer cycle, DQSx enters a preamble and a postamble state. The DQSx signals

are mapped to the following data bytes: DQS0 to DQ0.. DQ7, DQS1 to DQ8.. DQ15, DQS2 to

DQ16..DQ23, DQS3 to DQ24.. DQ31.

DQ31.. DQ0

I/O

Data Input/Output

: The DQx signals form the 32 bit wide data bus. At READ cycles the pins are

outputs and during WRITE cycles inputs. The data is transferred at both edges of the DQSx signals.

DM3.. DM0

Input

Input Data Mask

: The DM signals are input mask signal for WRITE data. They mask off a complete

byte on the data bus. DMx = 1 prevents the corresponding byte from being written. DM3 corresponds

to DQ31..DQ24, DM2 to DQ23..DQ16, DM1 to DQ15..DQ8, DM0 to DQ7..DQ0. DM signals are

sampled on both edges of DQS.

Although DM pins are input-only, the DM loading is designed to match that of DQ and DQS pins.

Vref

Input

Voltage Reference

: Vref is the reference voltage input signal.

VDD, VSS

Supply

Power Supply

: Power and Ground for the internal logic.

VDD = 2.5V +/- 5% for L4.5, -4.5 and -5

2.5V -5% < VDD < 2.9V for L3.6 and -3.6

2.5V < VDD < 2.9V for -3.0 and -3.3

VDDQ, VSSQ

Supply

IO Power Supply

: Isolated Power and Ground for the output buffers to provide improved noise

immunity. VDDQ = 2.5V +/- 5%

NC, RFU

-

Please do not connect No Connect, Reserved for Future Use pins.

MCL

-

Must be connected to low