120

TA-DA9000ES

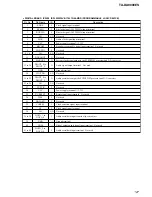

Pin No.

Pin Name

I/O

Description

44

CS0

O

Chip select signal output to the S-RAM

45

WE0

O

Write enable signal output to the S-RAM

46

VDDE

—

Power supply terminal (+3.3V)

47

WMD1

I

External memory wait mode setting terminal Fixed at “H” in this set

48

VSS

—

Ground terminal

49

WMD0

I

External memory wait mode setting terminal Fixed at “H” in this set

50

PAGE2

O

External memory page selection signal output terminal Not used

51

VSS

—

Ground terminal

52, 53

PAGE1, PAGE0

O

External memory page selection signal output terminal Not used

54

BOOT

I

Boot mode control signal input terminal Not used

55

BTACT

O

Boot mode state display signal output terminal Not used

56

BST

I

Boot strap signal input from the main system controller

57

MOD1

I

Operation mode setting terminal “L”: enhanced mode, “H”: normal mode

Fixed at “H” in this set

58

MOD0

I

Operation mode setting terminal “L”: single chip mode, “H”: can not use

Fixed at “L” in this set

59

EXLOCK

I

PLL lock error signal and data error flag input from the digital audio interface receiver

60

VDDI

—

Power supply terminal (+2.6V)

61

VSS

—

Ground terminal

62, 63

A17, A16

O

Address signal output terminal Not used

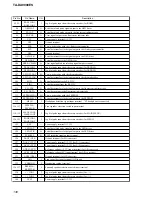

64 to 66

A15 to A13

O

Address signal output to the S-RAM

67

GP10

O

Not used

68

GP9

O

Read ready signal output to the main system controller

69

GP8

I

PCM audio data input from the digital audio interface receiver or i-link system controller

70

VDDI

—

Power supply terminal (+2.6V)

71

VSS

—

Ground terminal

72 to 75

D15 to D12

I/O

Two-way data bus with the S-RAM

76

VDDE

—

Power supply terminal (+3.3V)

77 to 80

D11 to D8

I/O

Two-way data bus with the S-RAM

81

VSS

—

Ground terminal

82 to 85

A9, A12 to A10

O

Address signal output to the S-RAM

86

TDO

O

Simplicity emulation data output terminal Not used

87

TMS

I

Simplicity emulation data input start and end terminal Not used

88

XTRST

I

Simplicity emulation non-sync break signal input terminal Not used

89

TCK

I

Simplicity emulation clock signal input terminal Not used

90

TDI

I

Simplicity emulation data input terminal Not used

91

VSS

—

Ground terminal

92 to 97

A8 to A3

O

Address signal output to the S-RAM

98, 99

D7, D6

I/O

Two-way data bus with the S-RAM

100

VDDI

—

Power supply terminal (+2.6V)

101

VSS

—

Ground terminal

102 to 105

D5 to D2

I/O

Two-way data bus with the S-RAM

106

VDDE

—

Power supply terminal (+3.3V)

107, 108

D1, D0

I/O

Two-way data bus with the S-RAM

109, 110

A2, A1

O

Address signal output to the S-RAM

111

VSS

—

Ground terminal