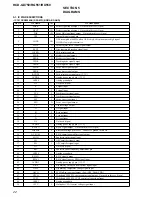

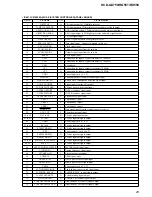

23

HCD-GX750/RG551/RX550

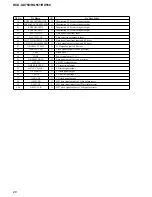

Pin No.

Pin Name

I/O

Pin Description

51

FILO

O

Master PLL (slave=digital PLL) filter signal output

52

FILI

I

Master PLL filter signal input

53

PCO

O

Master PLL charge pump signal output

54

AVDD5

—

Analog power supply pin (+3.3 V)

55

DDVROUT

O

DC/DC converter signal output

56

DDVRSEN

I

DC/DC converter output voltage monitor pin

57

AVSS5

—

Analog ground pin

58

DDCR

I

DC/DC converter reset pin

59

NC

—

Not used. (Open)

60

BCKI

I

D/A interface bit clock signal input

61

PCMDI

I

D/A interface serial data signal input (2’s COMP, MSB first)

62

LRCKI

I

D/A interface LR clock signal input

63

LRCK

O

D/A interface LR clock signal output f=Fs

64

VSS

—

Internal digital ground pin

65

PCMD

O

D/A interface serial data signal output (2’s COMP, MSB first)

66

BCK

O

D/A interface bit clock signal output

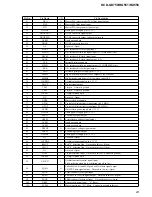

67

VDD

—

Internal digital power supply pin (+3.3 V)

68

EMPH

O

High when the playback disc has emphasis, low it has not

69

EMPHI

I

High when de-emphasis is ON, low when input OFF

70

IOVDD2

—

I/O digital power supply pin (+3.3 V)

71

DOUT

O

Digital signal output

72

TEST

I

Test pin Normally ground

73

TES1

I

Test pin Normally ground

74

IOVSS2

—

I/O digital ground pin

75

NC

—

Not used. (Open)

76

XVSS

—

Master clock ground pin

77

XTAO

O

Crystal oscillation circuit signal output (16.9 MHz)

78

XTAI

I

Crystal oscillation circuit signal input (16.9 MHz)

79

XVDD

—

Master clock power supply pin (+3.3 V)

80

AVDD1

—

Analog power supply pin (+3.3 V)

81

AOUT1

O

Lch analog signal output

82

VREFL

O

Lch reference voltage signal output

83

AVSS1

—

Analog ground pin

84

AVSS2

—

Analog ground pin

85

VREFR

O

Rch reference voltage signal output

86

AOUT2

O

Rch analog signal output

87

AVDD2

—

Analog power supply pin (+3.3 V)

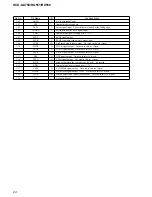

88

NC

—

Not used. (Open)

89

IOVDD0

—

I/O digital power supply pin (+3.3 V)

90

RMUT

O

Rch “0” detection flag Not used in this set. (Open)

91

LMUT

O

Lch “0” detection flag Not used in this set. (Open)

92

NC

—

Not used. (Open)

93

XTSL

I

Crystal selection input Not used in this set. (Connect to ground.)

94

IOVSS0

—

I/O digital ground pin

95

XTACN

I

Oscillation circuit control signal input

Self-oscillation when high, oscillation stop when low

96

SQSO

O

Subcode Q 80-bit and PCM peak and level data signal output

CD TEXT data signal output Not used in this set. (Open)

97

SQCK

I

SQSO readout clock signal input

98

SBSO

O

Subcode P to W serial signal output Not used in this set. (Open)

99

EXCK

I

SBSO readout clock signal input Not used in this set. (Open)

100

XRST

I

System reset signal input “L”: Reset

101

SYSM

I

Mute signal input “H”: Mute Connect to ground in this set.