29

29

HCD-GNX60/GNX70/GX9900

HCD-GNX60/GNX70/GX9900

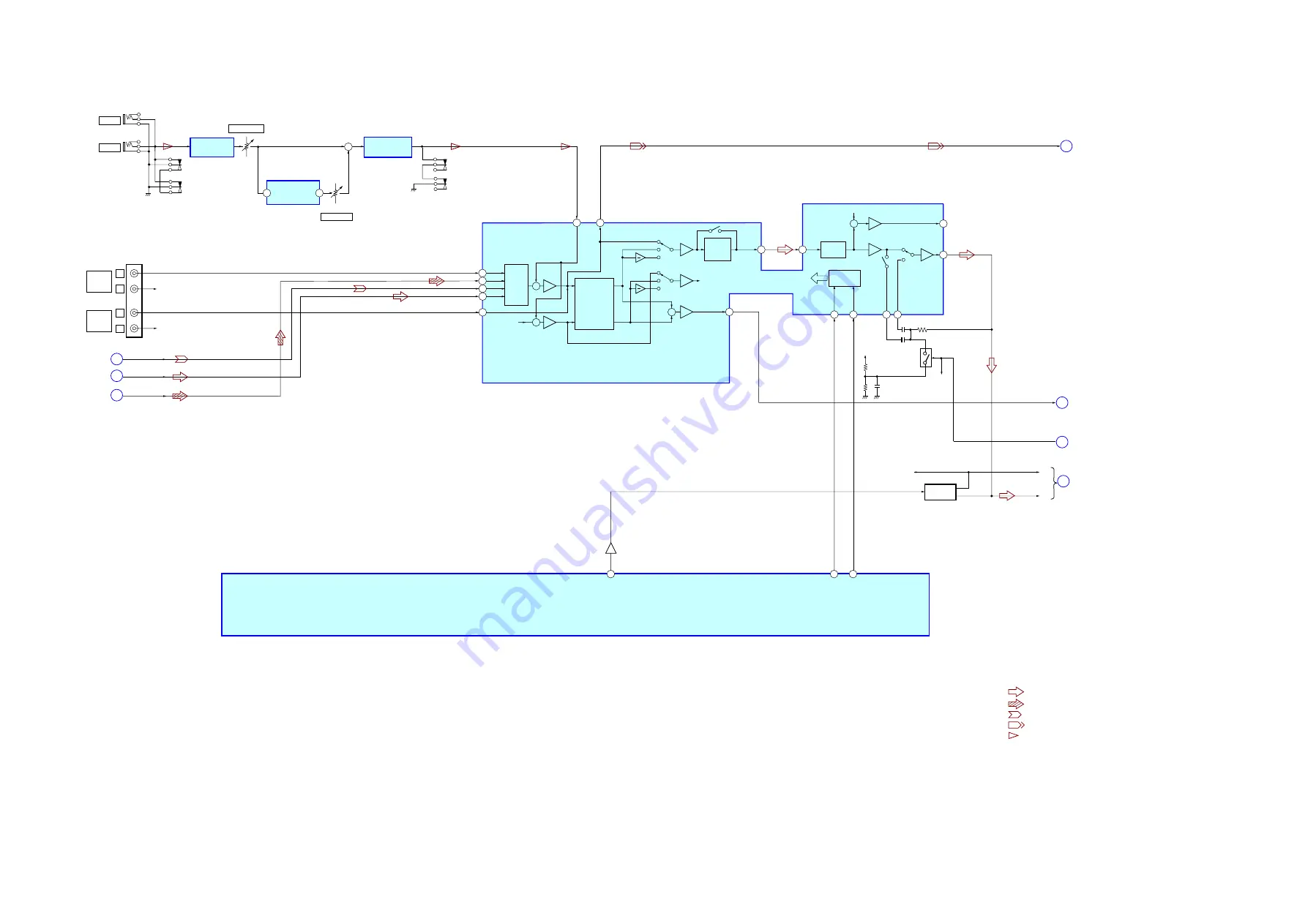

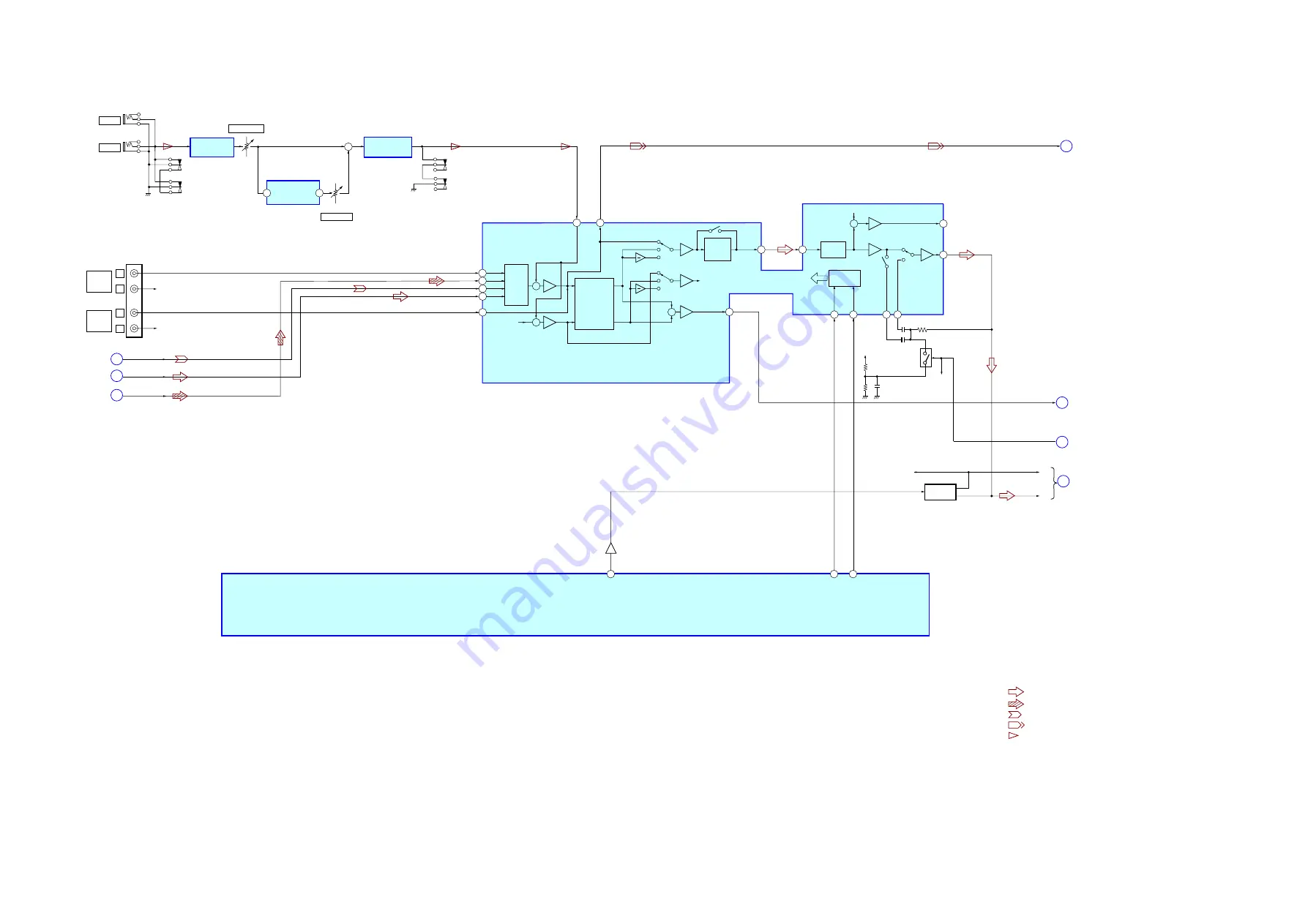

7-4. BLOCK DIAGRAM – MAIN SECTION –

J101

C

(Page 28)

(Page 28)

D

(Page 28)

E

R-CH

VOLUME

CONTROL

CPU

INTERFACE

INPUT

SELECT

SWITCH

SURROUND OR

DPL BUFFER

MID/

BASS &

TREBLE

R-CH

R-CH

COMMAND

TOUT1

OUT1

VOLIN1

+

Q101

R-CH

R-CH

SPEANA

DBFB F/B

F-R

F-L

+

+

+

RV1100

MIC AMP

IC1100 (2/2)

INPUT SELECT SWITCH,

GRAPHIC EQUALIZER CONTROL,

ELECTRICAL VOLUME

IC101

SYSTEM CONTROL

IC401

(3/5)

INA1

INEX1

INC1

SAOUT

DATA

CLK

BB-A1

BB-B1

SWOUT

REC-OUT-L

R-CH

TC-PB-L

TAPE SECTION

TAPE SECTION

ST-L

(Page 27)

A

CD SECTION

CD-L

LINE MUTE

M61529-DATA

M61529-CLK

R-CH

J1101(1/3)

J1101(2/3)

L

R

MD/VIDEO

AUDIO

IN

L

R

TV

AUDIO

IN

2

14

15

24

18

22

16

21

6

3

5

INB1

IND1

4

19

MIC 2

MIC AMP

IC1100(1/2)

ECHO LEVEL

MIC LEVEL

17

8

MIC

RECB1

7

MIC OUT

C

A

B

C

A

B

A+9V

+

2

1

3

9

6

7

DIGTAL

ECHO

IC1101

LPF2

OUT

LPF1

IN

81

82

66

AMP

SECTION

H

G

F

(Page 30)

AMP

SECTION

(Page 30)

DISPLAY

SECTION

TAPE

SECTION

(Page 31)

MUTE

Q180, 181

Q544,545

BUFFER

J1100(1/3)

J1100(2/3)

J1101(3/3)

J1100(3/3)

MIC 1

: TUNER (FM/AM)

: CD

: TAPE PLAY

: RECORD

: MIC INPUT

• SIGNAL PATH

• R-CH is omitted due to same as L-CH.