- 43 -

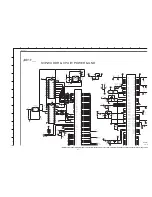

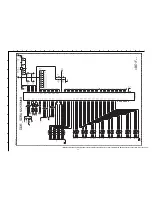

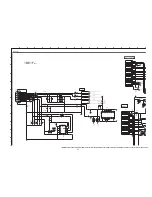

~ BE1F Board Schematic Diagram [ Micro Processor, Video/Audio Processor, Audio Amplifier, AV Switch, Tuner, Rear Input Terminals ] Page 8C/14 ~

11

22

Q

O

P

A

B

C

D

E

F

G

H

J

I

K

L

M

N

12

13

14

15

16

17

18

19

20

21

FE_+2V5

FE_+3V3

GND

GND

GND

FE_DQ[0-15]

011:H2

FE_D

ADD[0-12]

011:H5

FE_DBA0,FE_DBA1,FE_DCASB

,FE_DCKE,FE_DCLK,FE_DCLKB

,FE_DCSB

,FE_DQM0,FE_DQM1,FE_DQS0,FE_DQS1,FE_DRASB

,FE

_D

VREF

,FE_D

WEB

011:I6

JL7101

E

5

E17

F

5

F

1

7

G

5

G

1

7

T17

U

5

U

6

U

1

7

E

8

E

9

E10

E11

E12

E13

E

6

E

7

E14

E15

E16

H

5

A16

B16

A15

B15

A14

B14

A13

B13

D13

C13

D14

C14

D15

C15

D16

C16

D12

A9

B9

D8

A8

B8

A7

B7

A6

B6

D6

C6

D7

C7

C8

D9

A11

A12

C11

C12

C9

D10

C10

D11

B10

A10

B11

B12

Y17

W17

V17

AA17

AA16

Y16

W16

V16

AA15

A1

B2

A2

B3

A3

C4

B4

A4

A5

D5

F4

N4

P2

G2

R2

G1

K3

V1

C1

Y1

P3

B1

E4

UPD61123F1-100-KA3-A

IC7100

DQ15

A16

DQ14

B16

DQ13

A15

DQ12

B15

DQ11

A14

DQ10

B14

DQ9

A13

DQ8

B13

DQ7

D13

DQ6

C13

DQ5

D14

DQ4

C14

DQ3

D15

DQ2

C15

DQ1

D16

DQ0

C16

D

ADD13

D12

D

ADD12

A9

D

ADD11

B9

D

ADD10

D8

D

ADD9

A8

D

ADD8

B8

D

ADD7

A7

D

ADD6

B7

D

ADD5

A6

D

ADD4

B6

D

ADD3

D6

D

ADD2

C6

D

ADD1

D7

D

ADD0

C7

DBA1

C8

DBA0

D9

UDQM

A11

UDQS

A12

LDQM

C11

LDQS

C12

DCSB

C9

DRASB

D10

DCASB

C10

D

WEB

D11

DCKE

B10

DCLK

A10

DCLKB

B11

D

VREF

B12

VDI_D7 / PPOR

T121

Y17

VDI_D6 / PPOR

T120

W17

VDI_D5 / PPOR

T119

V17

VDI_D4 / PPOR

T118

AA17

VDI_D3 / PPOR

T117

AA16

VDI_D2 / PPOR

T116

Y16

VDI_D1 / PPOR

T115

W16

VDI_D0 / PPOR

T114

V16

VDI_VCK / PPOR

T113

AA15

STP0_D

A

T7 / PPOR

T8

A1

STP0_D

A

T6 / PPOR

T7

B2

STP0_D

A

T5 / PPOR

T6

A2

STP0_D

A

T4 / PPOR

T5

B3

STP0_D

A

T3 / PPOR

T4

A3

STP0_D

A

T2 / PPOR

T3

C4

STP0_D

A

T1 / PPOR

T2

B4

STP0_D

A

T0 / PPOR

T1

A4

STP0_EN / PPOR

T9

A5

STP0_CLK / PPOR

T0

D5

REGB / PPOR

T34

F4

IO

WRB / PPOR

T31

N4

IORDB / PPOR

T30

P2

INP

A

CKB / PPOR

T33

G2

GPIO_VS1B / PPOR

T28

R2

GPIO_RESET / PPOR

T32

G1

GPIO_IREQB / PPOR

T24

K3

GPIO_CD1B / PPOR

T26

V1

GPIO_CD2B / PPOR

T35

C1

PCE1B(CE2B_2) / PPOR

T36

Y1

PCE0B(CE2B_1) / PPOR

T27

P3

IOSI16B / PPOR

T25

B1

STP1

STR

T

/

PPOR

T38

E4

VDD3

E5

VDD3

E17

VDD3

F5

VDD3

F17

VDD3

G5

VDD3

G17

VDD3

T17

VDD3

U5

VDD3

U6

VDD3

U17

VDD2

E8

VDD2

E9

VDD2

E10

VDD2

E11

VDD2

E12

VDD2

E13

VDD1

E6

VDD1

E7

VDD1

E14

VDD1

E15

VDD1

E16

VDD1

H

0uH

FB7102

FE_+2V5_DDR

0uH

FB7104

FE_REGB

012:D2

FE_CI1_RSTB

012:D1

FE_IO

WRB

012:B10;012:D1

FE_IORDB

012:D1

FE_AVC_656CLK,FE_AVC_656[0-7]

013:N3

FE_CI1_VS1B

012:M4

FE_CI1_IREQB

012:D3

FE_CI1_CD1B

012:M4

FE_CI1_CD2B

012:M4

10k

R7143

FE_+3V3

FE_CI_TSCLK,FE_CI_TSSYNC

,FE_CI_TSV

AL

012:B9

FE_CI1_INP

A

CKB

012:D3

47

R7102

47

R7109

47

R7111

47

R7112

FE_M_CKOUT,FE_M_SYNC,FE_M_VAL

010:E2;012:B5;013:N7;015:9K

FE_M_DATA[0-7]

012:B5;013:N7;015:9K

25V

10

C7117

105

0

FB7126

CHIP

0

FB7120

CHIP

0

FB7127

CHIP

0

FB7121

CHIP

0

FB7128

CHIP

0

FB7122

CHIP

0

FB7129

CHIP

0

FB7123

CHIP

0

FB7124

CHIP

0

FB7125

CHIP

10V

4.7

2012

C7101

0.1

C7110

0.1

C7111

0.1

C7112

0.1

C7113

0.1

C7114

0.1

C7115

0 . 1

C7121

0 . 1

C7122

0 . 1

C7123

0 . 1

C7124

0 . 1

C7125

0 . 1

C7126

0.1

C7127

FE

CI

TSV

AL

FE_CI_TSSYNC

FE_D

ADD[0]

FE_D

ADD[1]

FE_D

ADD[2]

FE_D

ADD[3]

FE_D

ADD[4]

FE_D

ADD[5]

FE_D

ADD[6]

FE_D

ADD[7]

FE_D

ADD[8]

FE_D

ADD[9]

FE_D

ADD[10]

FE_D

ADD[11]

FE_D

ADD[12]

FE_DRASB

FE_DCSB

FE_DQS0

FE_DQM0

FE_DQS1

FE_DQM1

FE_DBA0

FE_DBA1

FE_DCKE

FE_D

WEB

FE_DCASB

FE_DCLKB

FE_DCLK

FE_D

ADD[13]

FE_D

VREF

FE_A

VC_656[0]

FE_A

VC_656[1]

FE_A

VC_656[2]

FE_A

VC_656[3]

FE_A

VC_656[4]

FE_A

VC_656[5]

FE_A

VC_656[6]

FE_A

VC_656[7]

FE_A

VC_656CLK

FE_DQ[0]

FE_DQ[1]

FE_DQ[2]

FE_DQ[3]

FE_DQ[4]

FE_DQ[5]

FE_DQ[6]

FE_DQ[7]

FE_DQ[8]

FE_DQ[9]

FE_DQ[10]

FE_DQ[11]

FE_DQ[12]

FE_DQ[13]

FE_DQ[14]

FE_DQ[15]

FE_M_D

A

TA[7]

FE_M_D

A

TA[6]

FE_M_D

A

TA[5]

FE_M_D

A

TA[4]

FE_M_D

A

TA[3]

FE_M_D

A

TA[2]

FE_M_D

A

TA[1]

FE_M_D

A

TA[0]

FE_M_V

AL

FE_M_CK

OUT

THESE CAP

A

CIT

ORS

T

O BE PLA

CED UNDERNEA

TH BGA

THESE CAP

A

CIT

ORS

T

O BE PLA

CED UNDERNEA

TH BGA

DIFFERENTIAL P

AIR

OF CLOCK SIGNALS

THIS CAP

A

CIT

OR

T

O BE

PLA

CED UNDERNEA

TH BGA

/ CTS1B

/ R

TS1B

UNCONTROL

Component Reference range

7100~7199

BE1F

8C/14

BE1F.-WAX3F