Semiconductor Group

9-7

1997-10-01

Power Saving Modes

C541U

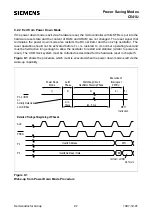

9.2.2 Exit from Power Down Mode

If the power down mode is exit via a hardware reset, the microcontroller with its SFRs is put into the

hardware reset state and the content of RAM and XRAM are not changed. The reset signal that

terminates the power down mode also restarts the RC oscillator and the on-chip oscillatror. The

reset operation should not be activated before

V

DD

is

restored

to

its

normal

operating level and

must be held active long enough to allow the oscillator to restart and stabilize (similar to power-on

reset). The USB clock system must be cotrolled as described for the hardware reset in chapter 5.

Figure 9-1 shows the procedure which must is executed when the power down mode is left via the

wake-up capability.

Figure 9-1

Wake-up from Power Down Mode Procedure

Invalid Address / Data

Invalid Address

00H

7BH

1st Instr. of ISR

P0

P2

PSEN

ALE

P3.2 / INT0

or

Activity Detected

on USB Bus

10

µ

s

min.

Power Down

Mode

Latch

Phase

typ. 5 ms

Watchdog Circuit

Oscillator Start-Up Phase

1)

2)

3)

4)

5)

Execution of

Interrupt at

007B

H

RETI

Instruction

Detailed Timing of Beginning of Phase 4

MCT03418

Summary of Contents for C541U

Page 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Page 7: ......

Page 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Page 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Page 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Page 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Page 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...