Semiconductor Group

6-72

1999-04-01

On-Chip Peripheral Components

C541U

The endpoint interrupt request register EPIRn contains the interrupt request flags of the different

endpoint specific interrupts. In general, the bits in EPIRn are reset by hardware after a EPIRn read

operation.

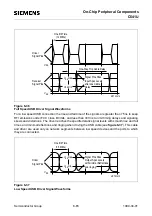

Endpoint Interrupt Request Register EPIRn, n=0-4 (Address C4H) Reset Value EPIR0 : 11H

Reset Value EPIR1 to EPIR4 : 10H

Bit

Function

ACKn

USB acknowledge

Bit ACKn=1 indicates a succesful action on the USB.

NACKn

USB not acknowledged

Bit NACKn is set for all unsuccessful actions on the USB.

RLEn

Read length error

Bit RLEn is automatically set if the number of bytes read by the USB does not

correspond to the packet length programmed by the CPU.

–

Reserved bit for future use. As this bit may return nonzero value, it must be

ignored in all read accesses.

DNRn

Data not ready

This bit is set by hardware if the UDC requires an access to USB memory, but no

buffer is available.

USB Read action : DNRn is set if UBF is not set.

USB Write action : DNRn is set if UBF is set.

NODn

No data

This bit indicates an incorrect CPU read or write access to USB memory. It is set

if the CPU processes a read access to an empty USB buffer or a write access to

a full buffer. NODn is also set if the direction is write (DIRn=0 for USB write

access) and the CPU tries to write to the USB memory buffer.

EODn

End of data

USB Read action : EODn is set if the CPU has written a programmable number

(MaxLen) of bytes in the transmit buffer. As a result, the buffer

is full and no more write actions from the CPU are allowed.

USB Write action: EODn is set if the CPU has read a programmable number

(USBLen) of bytes out of the receive buffer. As a result, the

buffer is empty now and no more read actions from the CPU

are allowed.

MSB

LSB

EPIRn

ACKn

NACKn

RLEn

–

DNRn

NODn

EODn

SODn

7

6

5

4

3

2

1

0

Bit No.

r

r

r

r

r

r

r

r

C4H

For accessing EPIRn, SFR EPSEL must be 0nH

.

Summary of Contents for C541U

Page 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Page 7: ......

Page 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Page 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Page 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Page 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Page 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...