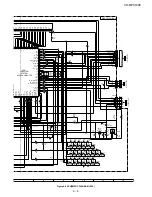

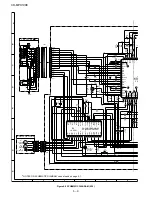

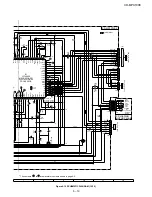

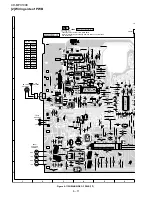

CD-MPX100E

6 – 7

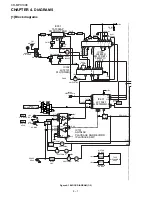

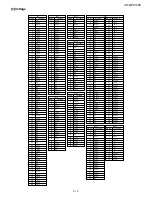

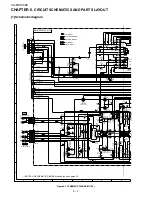

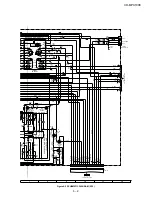

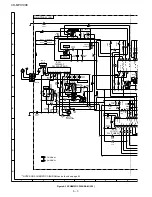

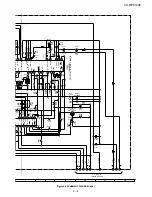

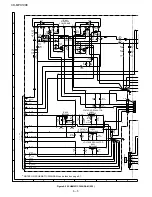

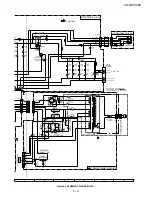

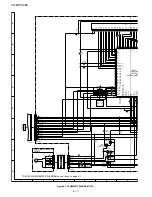

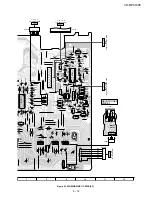

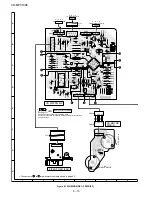

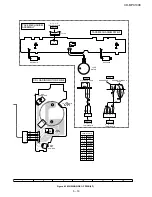

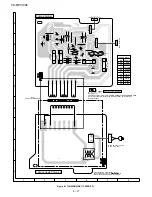

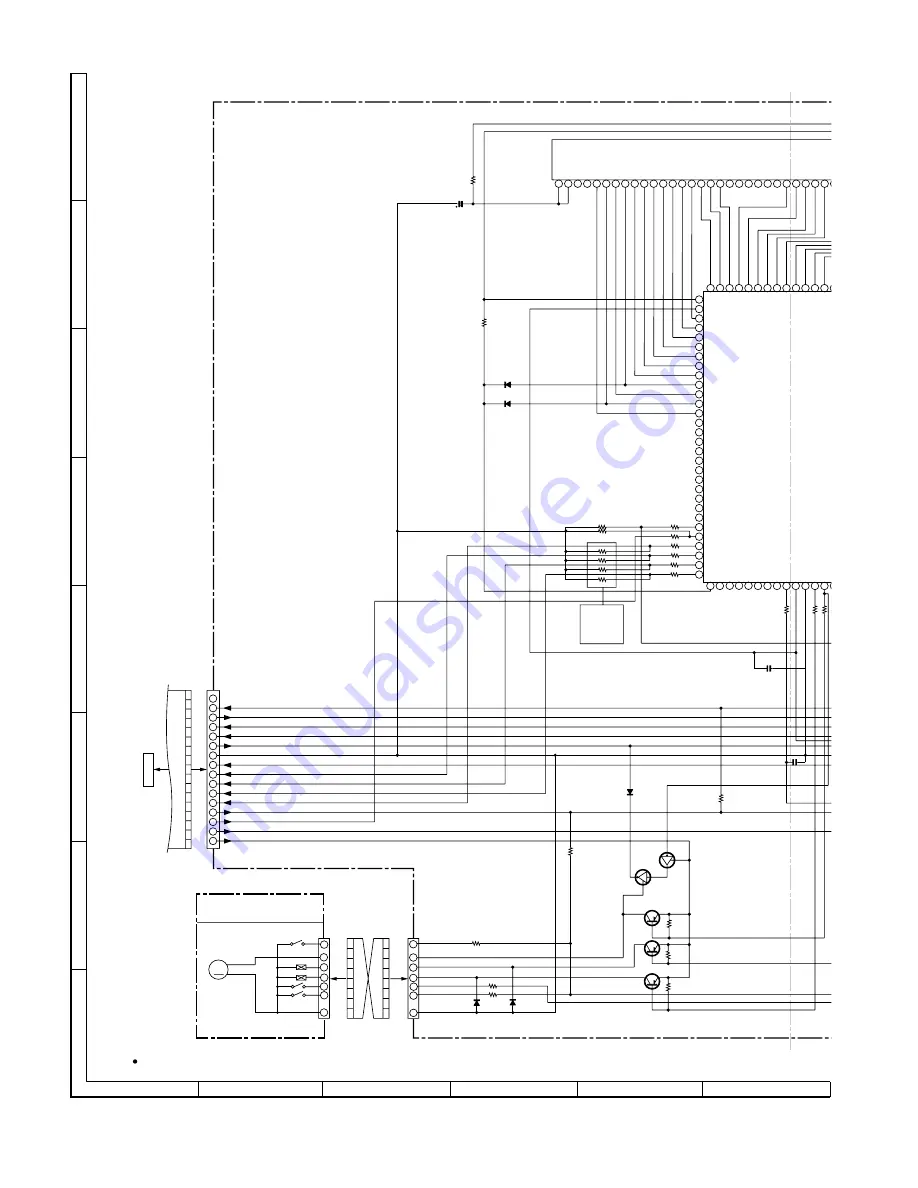

Figure 6-7 SCHEMATIC DIAGRAM (7/10)

M_+13V

CNP702A

R756

D707

D708

R757

R758

D702

R750

D704

C721

R747

FL701

IC701

R746

R752

R791

R794

R793

R792

R745

R743

R741

R742

R753

R744

R730

R732

R731

R733

R763

C716

D706

R759

Q707

Q708

Q709

Q710

R760

R761

R762

Q711

CNP701A

FFC701

FFC702

C732

680

1N4148H

1K

10K

10K

10K

10K

10K

1/50

1K

10K

KRA107 S

1N4148H

MOTOR DRIVER

MOTOR DRIVER

MOTOR

DRIVER

KRC104 S

680

2.2K

47K

1.5

1K

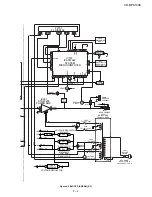

IXA057AW

3

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81 82 83 84 85 86 87 88 89 90 91 92 93 9

1K

1K

1K

10K

1N4148H

5.6K

8.2K

1K

KTA1273 Y

KTA1273 Y

10K

10K

0.022

1N4148H

1N4148H

4.7K

4.7K

10K

KTA1273 Y

NX

NX

NX

NX

NX

NX

/T2

/PLAY

S9

S8

DI

DO

- 20dB

SP_DET

CLK

CE

T_BIAS

T_T1/T2

REC/PLAY

D_GND

SP_RLY

+B_PROTECT

M_+13V

SW_5V

S_MUTE

T_MOTOR

S7

S6

S5

S4

G8

G9

RDS_RST(KARA_LATCH)

NS_SW1

ILLU_LED

VDD

VSS

T_SOL_A

S3

S2

S1

G11

G10

AC_RLY

T_T1

T

SOL

B

NS_SW2

SP_RLY

-20dBATT

NO USE

S20/(DIST 1)

NO USE

RDS

READY(MIC

SW)

NO USE

NO USE

NO USE

NO USE

NO USE

RESET

NO USE

NO USE

NO USE

NO USE

VLOAD

VDD

S17/(DIST 4)

S16

S15

S14

S19/(DIST 2)

S18/(DIST 3)

S10

S11

S12

S13

T_REC

T_BIAS

DIST

RDS_RDCL

RDS_RDDA

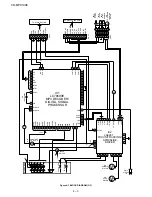

NP

NP

F2

F2

P20

P19

P18

P17

P16

P15

P14

P13

P12

P11

P10

P09

P08

P07

P06

P05

P04

P03

P02

45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

5

7

2

1

1

4

8

6

9

10

11

12

13

14

15

16

16

3

SOL

SOL

T2 RUN

+MTR

SOL2

SOL1

T1 RUN

GND

F_REC

+

-

M

3

2

2

3

4

5

6

7

7

1

1

7

7

1

1

6

5

4

CNP701B

6-2

1

0-H

TO

MAIN

PWB

TAPE MECHANISM

PWB-F

1

2

3

2

1

3

SYSTEM

MICROCOMPU

+B

+B

+B

+B

+B

+B

+B

SOLENOIDE

DRIVER

0.022

A

B

C

D

E

F

G

H

1

2

3

4

5

6

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

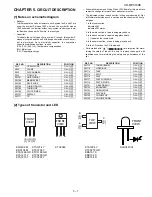

Summary of Contents for CD-MPX100E

Page 20: ...CD MPX100E 5 2 3 Waveforms of CD circuit ...

Page 52: ...CD MPX100E 8 10 M E M O ...

Page 81: ...CD MPX100E M E M O 29 ...

Page 82: ...CD MPX100E M E M O 30 ...

Page 83: ...CD MPX100E M E M O 31 ...