5-18

Trip and Target Logic

Date Code 20010625

SEL-311L Instruction Manual

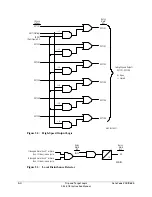

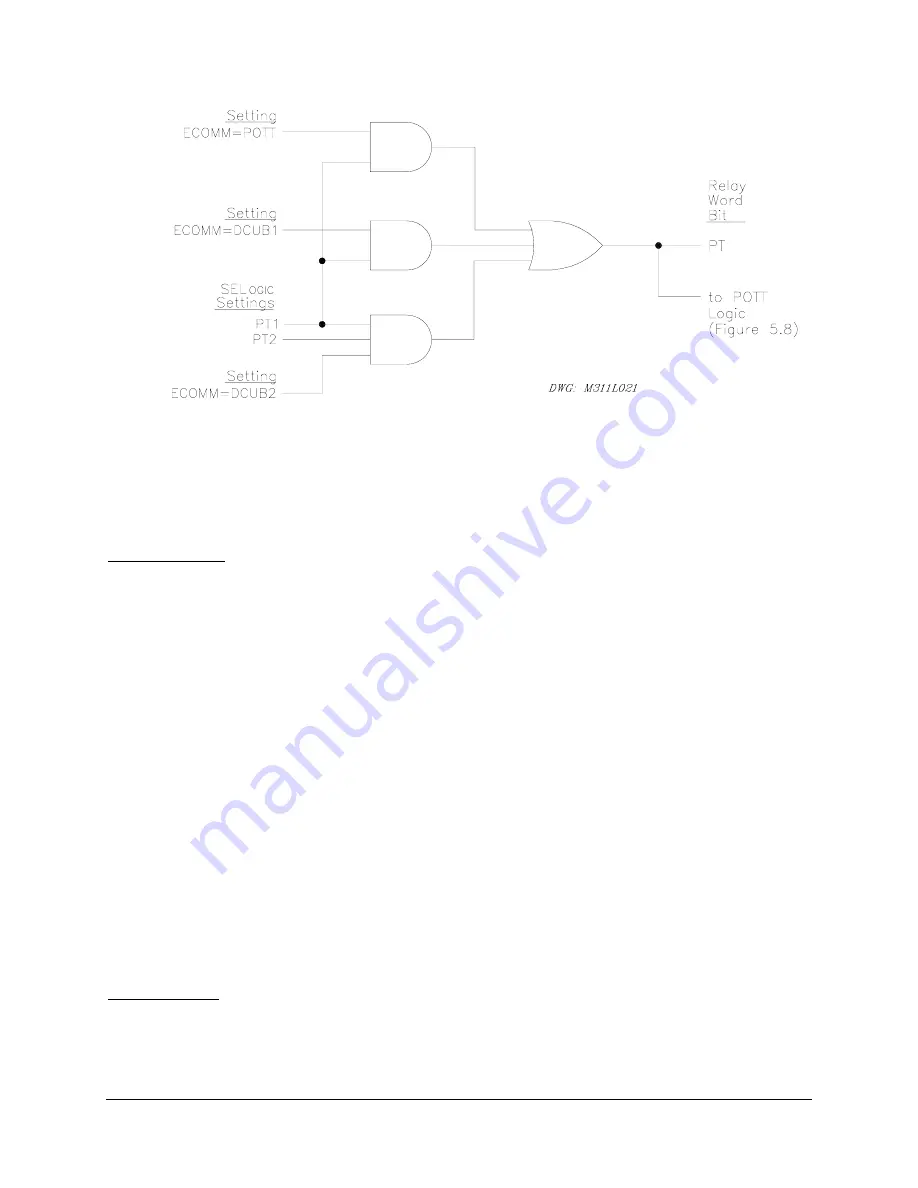

Figure 5.7: Permissive Input Logic Routing to POTT Logic

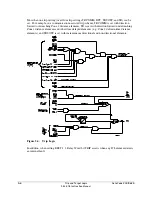

Also note that SEL

OGIC

control equation setting PT1 in Figure 5.9 is routed to control Relay

Word bit PTRX if enable setting ECOMM = POTT. Relay Word bit PTRX is the permissive trip

receive input into the trip logic in Figure 5.4.

Timer Settings

See

Section 9: Setting the Relay

for setting ranges.

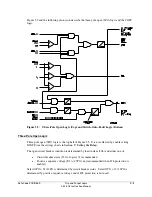

Z3RBD—Zone (Level) 3 Reverse Block Delay

Current-reversal guard timer—typically set at 5 cycles.

EBLKD—Echo Block Delay

Prevents echoing of received PT for settable delay after dropout of local permissive elements in

trip setting TRCOMM—typically set at 10 cycles. Set to OFF to defeat EBLKD.

ETDPU—Echo Time Delay Pickup

Sets minimum time requirement for received PT, before echo begins—typically set at 2 cycles.

Set to OFF for no echo.

EDURD—Echo Duration

Limits echo duration, to prevent channel lockup—typically set at 4.0 cycles.

Logic Outputs

The following logic outputs can be tested by assigning them to output contacts. See

Output

Contacts

in

Section 7: Inputs, Outputs, Timers, and Other Control Logic

for more information

on output contacts.

Summary of Contents for SEL-311L

Page 6: ......

Page 8: ......

Page 26: ......

Page 54: ......

Page 144: ......

Page 216: ......

Page 252: ......

Page 302: ......

Page 338: ......

Page 480: ......

Page 484: ......

Page 486: ......

Page 502: ......

Page 532: ...12 28 Standard Event Reports and SER Date Code 20010625 SEL 311L Instruction Manual 4 ...

Page 552: ......

Page 554: ......

Page 574: ......

Page 576: ......

Page 596: ......

Page 602: ......

Page 628: ......

Page 656: ......

Page 662: ......

Page 664: ......

Page 688: ......

Page 700: ......

Page 716: ......

Page 722: ......

Page 734: ......