-95-

PIN

PORT

NAME

DESCRIPTION

I/O

1

OE1

CS1

PW392 Chip Select

I

2

A1

THERM2_DETECT

Temp. Sensor 2 Detection, H: Error, L: Normal

I

3

A2

LENS_SENS_C

Lens Shift Sensor (Left-Right Center), H: Center, L: Not Center

I

4

A3

LENS_SENS_L

Lens Shift Sensor (Left), L: End

I

5

A4

LENS_SENS_R

Lens Shift Sensor (Right), L: End

I

6

A5

LENS_SENS_D

Lens Shift Sensor (Down), L: End

I

7

A6

LENS_SENS_U

Lens Shift Sensor (Up), L: End

I

8

A7

THERM1_DETECT

Temp. Sensor 1 Detection, H: Error, L: Normal

I

9

A8

S_SW

S-Terminal Detection, L: Inserted

I

10

GND

GND

-

-

11

Y8

D7

Data Bus 7

O

12

Y7

D6

Data Bus 6

O

13

Y6

D5

Data Bus 5

O

14

Y5

D4

Data Bus 4

O

15

Y4

D3

Data Bus 3

O

16

Y3

D2

Data Bus 2

O

17

Y2

D1

Data Bus 1

O

18

Y1

D0

Data Bus 0

O

19

OE2

OE2

Output Enable2

I

20

Vcc

Vcc

-

-

PIN

PORT

NAME

DESCRIPTION

I/O

55

P28

D+ PULL-UP

USB D+ Pull-up Control

O

56

DVss

DVss

-

-

57

VREFN

VREFN

Reference Voltage Output

58

VCOM

VCOM

Opamp Bias Tap

59

VREFP

VREFP

Reference Voltage Output

60

Avss

Avss

-

-

61

AIN1

P-FAIL_1.8V

1.8V Power Failure Detection

AI

62

AIN2

P-FAIL_S-5V

S-5V Power Failure Detection

AI

63

AIN3

P-FAIL_1.2V

1.2V Power Failure Detection

AI

64

AIN4

P-FAIL_15V

15V Power Failure Detection

AI

65

AIN5

P-FAIL_S5V

S5V Power Failure Detection

AI

66

AIN6

P-FAIL_PJ

PJ-Net Power Failure Detection

AI

67

AIN7

THERM1

Temp Error Detection (Room)

AI

68

AIN8

THERM2

Temp Detection (TEMP C Blue Panel)

AI

69

AVdd33

AVdd33

-

-

70

DVdd33

DVdd33

-

-

71

XCS2

XCS2

Ext. Chip Select

O

72

P31

I/O_PJ_UART

PJ-Net Command (PW:TXD)

O

73

P32

PJ_I/O_UART

PJ-Net Command (PW:RXD)

I

74

P33

M_TXD

PJ-Net AirMouse TXD

O

75

P34

Not Used

I

76

P35

LENS_LR_PWM

Lens Shift Left/Right PWM Output, L: Move, H: Stop

O

77

P36

LENS_UD_PWM

Lens Shift Up/Dwon PWM Output, L: Move, H: Stop

O

78

P37

DAC_PWM

PWM for Fan Control

O

79

P38

NET_SW

PJ-Net Power On/Off

O

80

UVss

Uvss

-

-

81

DMINUS

DMINUS

USB D-

I/O

82

DPLUS

DPLUS

USB D+

I/O

83

UVdd33

UVdd33

-

-

84

DVdd25

DVdd25

-

-

85

XCS3

XCS3

Ext. Chip Select

O

86

DVss

DVss

-

-

87

DVss

DVss

-

-

88

RSTMSK

RSTMSK

Internal Reset Mask

I

89

DVdd33

DVdd33

-

-

90

DVss

DVss

-

-

91

P11

SCLK_I/O

Configration Clock

O

92

P12

SDATA_I/O

Configration Data / FPGA Data Out

O

93

P13

SDTO_I/O

FPGA Data In

I

94

P14

BOX_SW

PJ-Net In

I

95

DVss

DVss

-

-

96

DVss33

DVss33

-

-

97

P15

W_RC_SW

Wired RC Detectionm H: Not Inserted, L: Inserted

I

98

P16

PRODUCT_OPT

I

99

P17

INT_I/O

Configration Status

I

100

P18

DONE_I/O

Configration Process End Signal

I

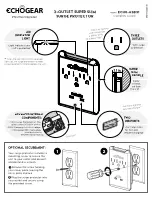

Parallel Bus Input Expander Port Functions (TC74LCX541, IC1881)

Control Port Functions

Summary of Contents for PLC-ET30L

Page 97: ... 97 IC Block Diagrams BA7078 Sync Seperator IC5321 FA7701V Switching Controller IC5641 ...

Page 98: ... 98 IC Block Diagrams HIN202EIB RS 232C Driver IC3801 ISL51002 10 bit Video A D IC6201 ...

Page 100: ... 100 IC Block Diagrams LM4889 Audio Output IC5121 NJW1141 Audio Control IC5001 ...

Page 102: ... 102 IC Block Diagrams THS7347IPHPR PC1 PC2 SW IC5201 ...

Page 108: ... 108 Parts Location Diagrams KF7 ET30L00 Polarized glass GB L06 L06 ...

Page 137: ...Key No Part No Description Key No Part No Description KF7 ET30L00 137 Electrical Parts List ...

Page 138: ... KF7AL Apr 2008 DC 300 Printed in Japan SANYO Electric Co Ltd ...