RTD Embedded Technologies, Inc.

| www.rtd.com

24

DM35418HR/DM35218HR

User’s Manual

BDM-610010041 Rev F

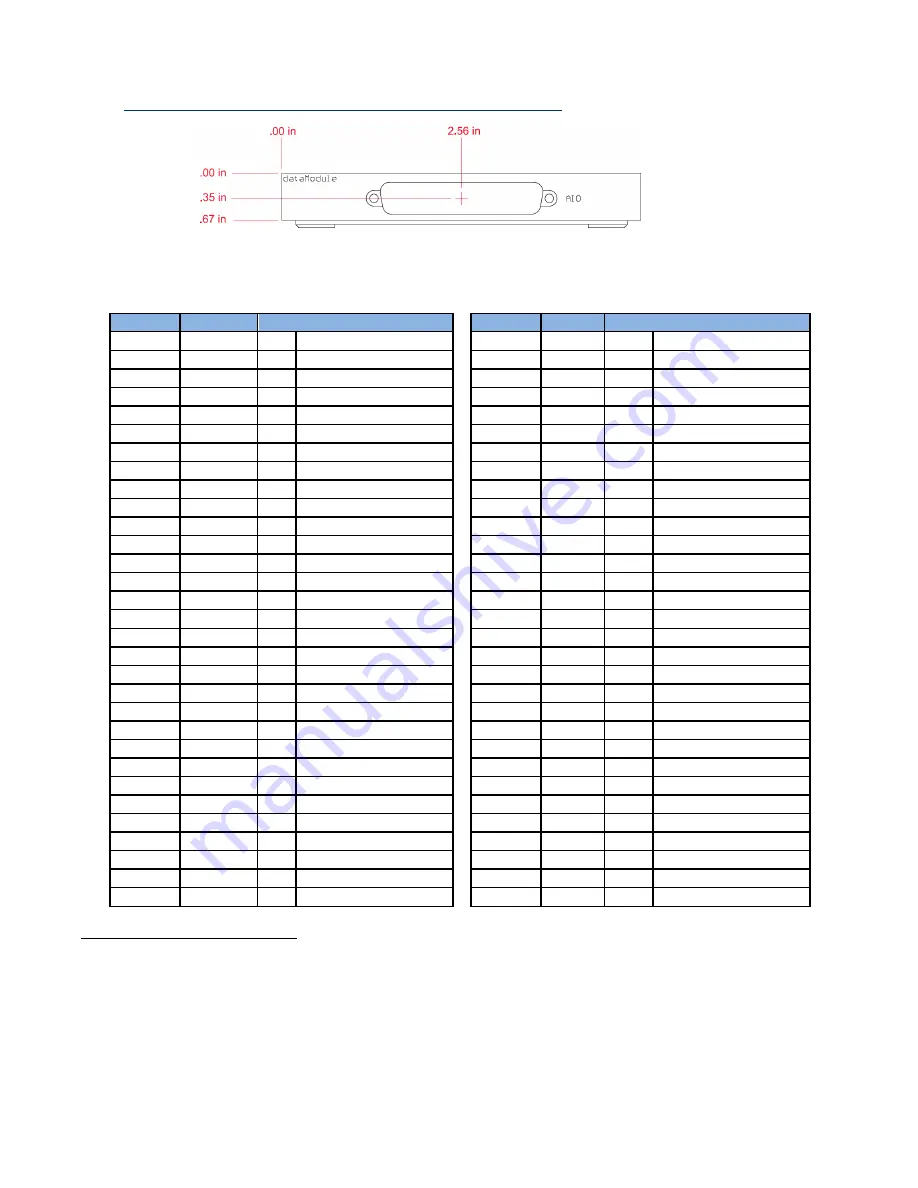

Analog I/O and SyncBus Connector - 62-pin High Density “D” Female Connector

Connector Part #:

VALCONN HDB-62S

Example Mating Connector:

VALCONN HDB-62P

Table 13: IDAN- DM35218 62-Pin High Density "D" Connector

IDAN Pin#

Signal

DM35218 Pin #

1

ADC0.0+

CN4

1

2

GND

CN4

4

3

GND

CN4

7

4

ADC2.0-

CN4

10

5

ADC3.0+

CN4

13

6

GND

CN4

16

7

GND

CN4

19

8

Reserved

CN4

22

9

Reserved

CN4

25

10

GND

CN4

28

11

GND

CN4

31

12

GND

CN4

34

13

DAC2.0

CN4

37

14

GND

CN4

40

15

Reserved

CN4

43

16

GND

CN4

46

17

+5V Analog

1

CN4

49

18

GND

CN5

12

19

SYNC1+

CN5

5

20

GND

CN5

4

21

SYNC0+

CN5

1

22

ADC0.0-

CN4

2

23

ADC1.0+

CN4

5

24

GND

CN4

8

25

GND

CN4

11

26

ADC3.0-

CN4

14

27

Reserved

CN4

17

28

GND

CN4

20

29

GND

CN4

23

30

Reserved

CN4

26

31

Reserved

CN4

29

Table 13: IDAN- DM35218 62-Pin High Density "D" Connector

IDAN Pin#

Signal

DM35418 Pin #

32

GND

CN4

32

33

DAC1.0

CN4

35

34

GND

CN4

38

35

Reserved

CN4

41

36

GND

CN4

44

37

Reserved

CN4

47

38

GND

CN4

50

39

SYNC3-

CN5

14

40

SYNC1-

CN5

6

41

SYNC2-

CN5

10

42

SYNC0-

CN5

2

43

GND

CN4

3

44

ADC1.0-

CN4

6

45

ADC2.0+

CN4

9

46

GND

CN4

12

47

GND

CN4

15

48

Reserved

CN4

18

49

Reserved

CN4

21

50

GND

CN4

24

51

GND

CN4

27

52

Reserved

CN4

30

53

DAC0.0

CN4

33

54

GND

CN4

36

55

DAC3.0

CN4

39

56

GND

CN4

42

57

Reserved

CN4

45

58

GND

CN4

48

59

SYNC3+

CN5

13

60

GND

CN5

15

61

SYNC2+

CN5

9

62

GND

CN5

7

1

Analog voltage rail can supply up to 1A. Customer must ensure that the current limit is not exceeded.