Remote Control Basics

R&S

®

NRPxxT(N)

143

User Manual 1177.6023.02 ─ 08

The highest level is formed by the status byte register (STB) and the associated ser-

vice request enable (SRE) register.

The status byte register (STB) receives its information from:

●

Standard event status register (ESR)

●

Associated standard event status enable register (ESE)

●

SCPI-defined operation status register

●

Questionable status register, which contains detailed information on the device.

11.3.2

Structure of a SCPI Status Register

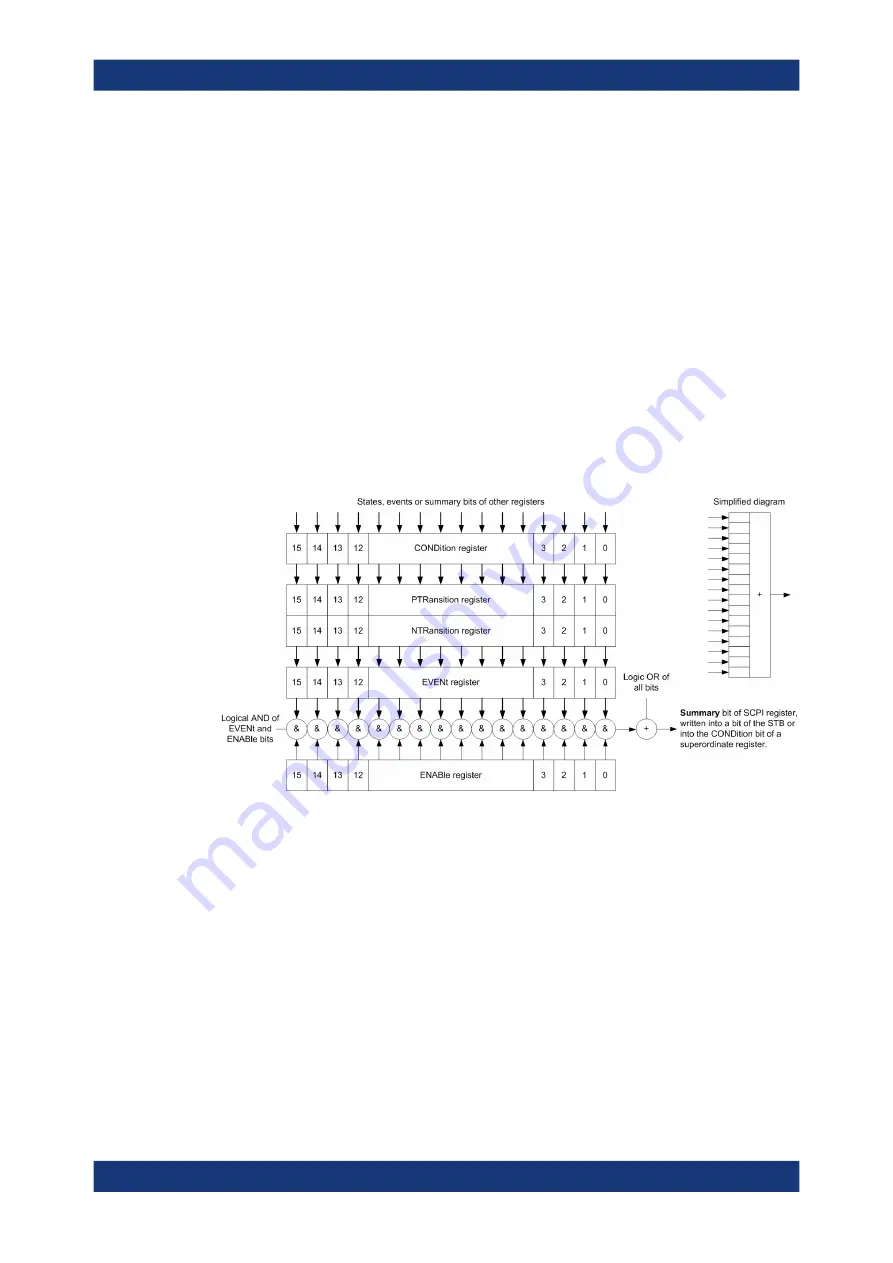

Each SCPI register consists of five 16-bit registers that have different functions, see

. The individual bits are independent of each other, i.e. each hardware sta-

tus is assigned a bit number which is the same for all five registers. Bit

15, the most-

significant bit, is set to 0 in all registers, thus preventing problems some controllers

have with the processing of unsigned integers.

Figure 11-2: Standard SCPI status register

CONDition status register part

The five parts of a SCPI register have different properties and functions:

The

CONDition

part is written into directly by the hardware or the sum bit of the next

lower register. Its contents reflect the current instrument status. This register part can

only be read, but not written into or cleared. Its contents are not affected by reading.

PTRansition / NTRansition status register part

The two transition register parts define which state transition of the

CONDition

part

(none, 0 to 1, 1 to 0 or both) is stored in the

EVENt

part.

Status Reporting System