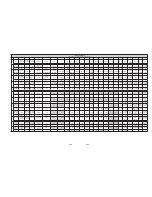

7. GPS BLOCK DIAGRAM

SAW Filter

GPS ANTENNA

IC1300 – GPS CHIP

FILTER

IC600 – CPU

5 V ANT

UART

LDO

X1300(32.768 kHz)

X1301(26 MHz)

3.3 V

TCXO or Crystal

Optional RTC Crystal

UART

UBX-G6010

Integrated LNA

RF Front-End

Fractional

N Synthesizer

Digital IF Filter

SRAM

ROM Code

ARM7TDM-S

®

Power MGM

RTC

Backup RAM

Interfaces

GPS/GALILEO

Engine

GPIO

CPU

(NetLogic microsystems)

AU1320

I2C

LCDC

PSC

2-46

2-45

Summary of Contents for LAN5200WR1

Page 17: ...2 12...

Page 28: ...2 34 2 33 BLOCK DIAGRAMS 1 FUNCTION BLOCK DIAGRAM...

Page 49: ...PRINTED CIRCUIT BOARD DIAGRAMS 1 FRONT P C BOARD 2 75 2 76 TOP VIEW...

Page 50: ...BOTTOM VIEW 2 77 2 78...

Page 51: ...2 MAIN P C BOARD 2 79 2 80 TOP VIEW...

Page 52: ...BOTTOM VIEW 2 81 2 82...

Page 53: ...2 83 2 84...