5G Module Series

RM505Q-AE Hardware Design

RM505Q-AE_Hardware_Design 37 / 79

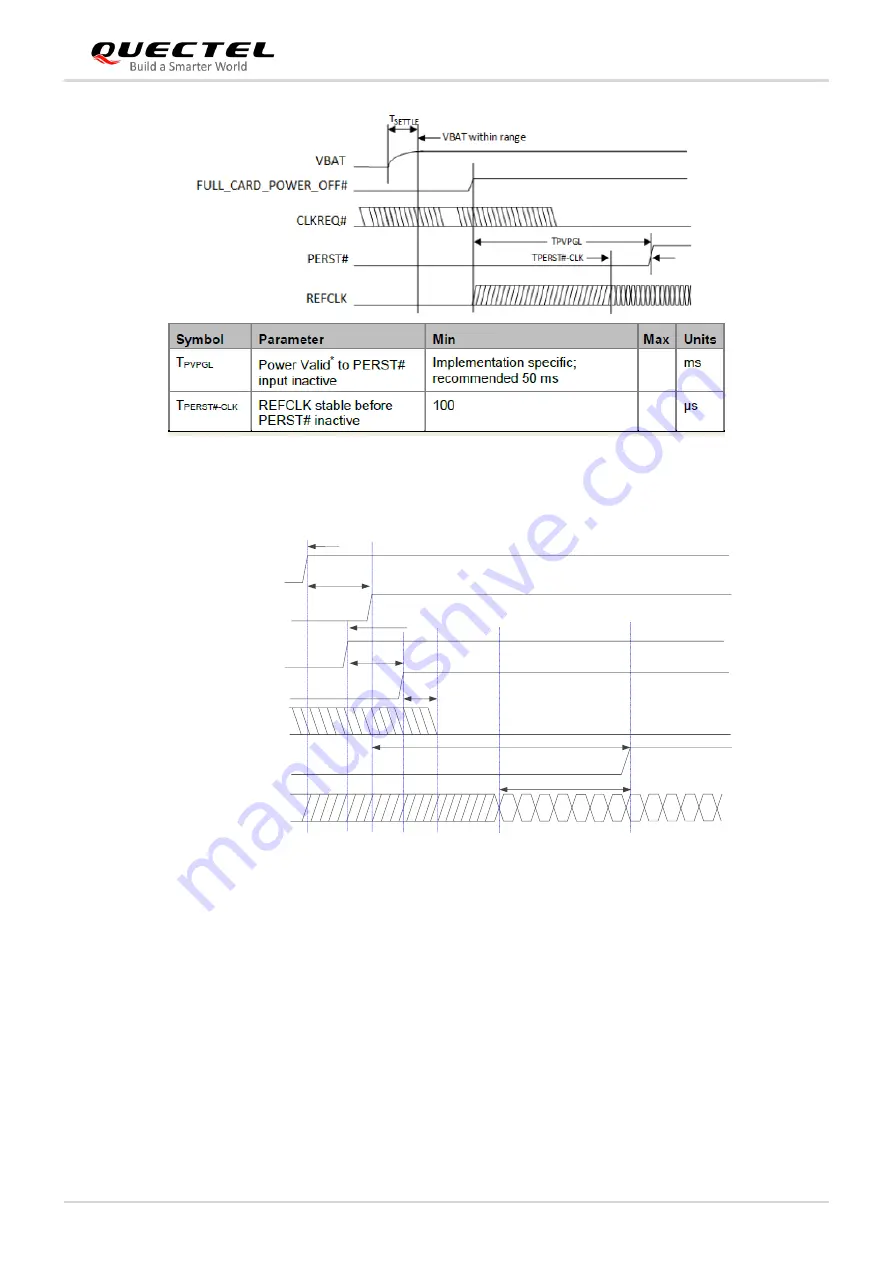

Figure 19: PCIe Power-on Timing Requirements of M.2 Specification

VCC

Module power-on or insertion detection

PICE_REFCL K

RFFE_ VIO _1V8

Syst em turn-on and booting

t

turn-on

68 ms

23 ms

PICE_RST_N

TPERST#_CLK

>

100 us

TPVPGL

100 ms

V

IH

1.19 V

t

power -on

FUL L_CARD_ POWER_OFF

RESET_N

Figure 20: PCIe Power-on Timing Requirements of the Module

The following principles of PCIe interface design should be complied with, so as to meet PCIe

specification.

⚫

Keep the PCIe data and control signals away from sensitive circuits and signals, such as RF, audio,

crystal and oscillator signals.

⚫

Add a capacitor in series on Tx/Rx traces to prevent any DC bias.

⚫

Keep the maximum trace length less than 300 mm.

⚫

Keep the length matching of each differential data pair (Tx/Rx) less than 0.7 mm for PCIe routing

traces.

⚫

Keep the differential impedance of PCIe data trace as 85

Ω ±10 %.