Circuit Descriptions, Abbreviation List, and IC Data Sheets

9.

9.4.3

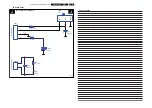

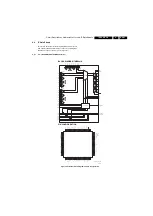

SXGA LCD TV Controller with Video Decoder and 8-bit Dual LVDS Transmitter, MST9WxxLD (U7)

Figure 9-3 Internal block diagram and pin configuration

PIN CONFIGURATION M

S

T9W55

H_17490_029.ep

s

291007

Pin 1

13

14

17

18

21

23

25

27

28

30

32

34

36

39

41

43

15

16

19

20

22

24

26

29

31

33

35

37

38

40

42

44

45

46

47

48

50

51

52

49

RXCKP

GND

RX0N

RX0P

AVDD_DVI

RX1N

RX1P

RX2P

REXT

DDCD_CK

VSYNC1

VCLAMP

REFM

BIN1M

GND

RX2N

AVDD_DVI

DDCD_DA

HSYNC1

RMID

REFP

BIN1P

SOGIN1

GIN1P

GIN1M

RIN1P

RIN1M

BIN0M

BIN0P

GIN0M

GIN0P

SOGIN0

RIN0M

RIN0P

HSYNC0

VSYNC0

VSYNC2

BIN2P

BIN2M

SOGIN2

GIN2P

GIN2M

RIN2P

RIN2M

C1

Y1

C0

Y0

1

2

3

4

5

7

9

11

6

8

10

12

53

54

55

56

57

59

61

63

58

60

62

64

CVBS2

CVBS1

VCOM1

CVBS0

VCOM0

CVBSOUT

GND

SIF0M

SIF0P

AVDD_SIF

SIF1P

77

78

81

82

85

87

89

91

92

94

96

98

10

0

10

3

10

5

10

7

79

80

83

84

86

88

90

93

95

97

99

10

1

10

2

10

4

10

6

10

8

10

9

11

0

11

1

11

2

11

4

11

5

11

6

11

3

AU

VR

AN

P

AU

VR

EF

AVD

D

_A

U

AU

L0

AU

R0

AU

L1

AU

R1

AU

CO

M

AU

L3

AU

M

O

NO

BP

SR

N

C

AUO

UT

R

NC NC

AU

L2

AU

R2

AU

R3

BP

SL

NC

AU

OU

TL

AU

O

UT

S

NC NC NC NC NC NC NC

VD

DC

D

QS

[1

]

M

D

AT

A[1

5]

M

D

AT

A[

14

]

GN

D

MDA

TA[

13

]

MDA

TA

[12

]

VD

D

M

M

D

AT

A[1

1]

MD

ATA

[1

0]

M

DA

TA[

9]

MD

ATA

[8

]

GN

D

VDDM

M

DA

TA

[7

]

MD

AT

A[

6]

MD

AT

A[

5]

65

66

67

68

69

71

73

75

70

72

74

76

11

7

11

8

11

9

12

0

12

1

12

3

12

5

12

7

12

2

124

12

6

12

8

MD

ATA

[4

]

VD

D

M

MD

AT

A[

3]

MD

AT

A[

2]

MD

AT

A[

1]

MD

ATA

[0

]

M

VR

EF

D

QS

[0

]

D

QM

MC

LKF

180

179

176

175

172

170

168

166

165

163

161

159

157

154

152

150

178

177

174

173

171

169

167

164

162

160

158

156

155

153

151

149

148

147

146

145

143

142

141

144

DDCR_CK

PWM1

SAR3

SAR1

SDO

SDI

SCK

DDCR_DA

PWM0

SAR2

SAR0

CSZ

GND

VDDP

ALE

RDZ

WRZ

AD[7]

AD[6]

AD[5]

AD[4]

AD[3]

AD[2]

AD[1]

AD[0]

MADR[11]

MADR[10]

MADR[9]

MADR[8]

VDDC

GND

VDDM

MADR[7]

MADR[6]

MADR[5]

MADR[4]

MADR[3]

MADR[2]

192

191

190

189

188

186

184

182

187

185

183

181

140

139

138

137

136

134

132

130

135

133

131

129

MADR[1]

MADR[0]

WEZ

CASZ

AVDD_MEMPLL

VDDM

GND

RASZ

BADR[0]

244

243

240

239

236

234

232

230

229

227

225

223

221

218

216

214

242

241

238

237

235

233

231

228

226

224

222

220

219

217

215

213

212

211

210

209

207

206

205

208

AVD

D

_M

PL

L

XI

N

XO

UT

HWR

ES

ET

VD

D

P

DI

[1

4]

DI

[1

3]

DI

[1

2]

DI

[1

1]

256

25

5

254

25

3

252

25

0

248

246

25

1

249

247

245

204

203

202

20

1

200

198

196

194

199

197

195

193

MS T9W 55L

XXXXXXXXXXX

XXXXX

AU

VR

AD

N

VCOM2

CVBS3

RXCKN

MC

LK

Z

GN

D

VD

D

P

PWM2

DIGO[7]

DIGO[6]

DIGO[5]

DIGO[8]

DIGO[0]

VDDC

GND

VDDP

GP

IO

E[

1]

GP

IO

E[

2]

GP

IO

E[

3]

GND VDDP LV

B0

M

LV

B0

P

LV

B1

M

LV

B1

P

LV

B2

M

LV

B2

P

LV

BCK

M

LV

BC

KP

LV

B3

M

LV

B3

P

NC NC GND VDDP LV

A0

M

LV

A0

P

LV

A1

M

LV

A1

P

LV

A2

M

LV

A2

P

LV

AC

KM

LV

AC

KP

LV

A3

M

NC VDDP

PW

M

3

VD

D

C

AVD

D

_M

PL

L

DI

[9

]

DI

[4

]

DI

[1

0]

DI

[6

]

DI

[5

]

DI

[1

5]

DIGO[3]

DIGO[2]

DIGO[1]

IRIN

INT

DDCA_CK

DDCA_DA

DI

[8

]

LV

A3

P

NC

DIGO[4]

GN

D

SI

F1M

G

ND

VDDC DI

[7

]

VDDP DI

[3

]

DI

[2

]

DI

[1

]

DI

[0

]

IVS

YN

C

IH

SY

N

C

ID

E

IC

LK

GP

IO

E[

0]

AVDD_ADC

GND

MC

LK

BAD

R[

1]