Circuit Descriptions

7.

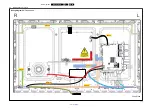

Figure 7-14 Power Architecture UHD50 - Back end

7.3.3

Low Voltage Differential Signalling

Figure 7-15 FHD100

Figure 7-16 UHD100

Figure 7-17 UHD50

19570_174_140723.eps

14-07-23

+12V

DC/DC

TPS5442

7DDA

U010U

+1V2

1V2-FPGA

FPGA LX25

(HDMI2,0) Boa

+3V3

+3V3

FPGA LX75

(PQ, NR, LC) A

+3V3

+2V5-BE

LDO

RT9187G

SP

U021B

+3V3

+3V3

+1V5-BE

DDR FPGA

1&2

19570_202_140822.eps

14-08-22

8xx9 series 48” - 55“

X050

X051

X055

SSB

Marvell

FHD

100 Hz

Samsung TCON

51

51

41p LVDS

51p LVDS

19570_203_140822.eps

14-08-22

9109 series 55” - 65”

X056

X060

X061

X056

X051

X054

X054

X051

X318

X053

UHD

Marvell

SSB

BOLT-ON

Samsung TCON

51

41

51p LVDS

51p LVDS

51p LVDS

X010

19570_204_140822.eps

14-08-22

9809 series 65” - 75”

BLD

PSU

BOLT-ON

X056

X060

X061

X056

X051

X054

X054

X051

X318

X053

75” only

UHD

Marvell

SSB

Samsung TCON

51p LVDS

51

41

51p LVDS

51p LVDS

X010