Setting Up

5-41

9161-A2-GH30-40

April 1999

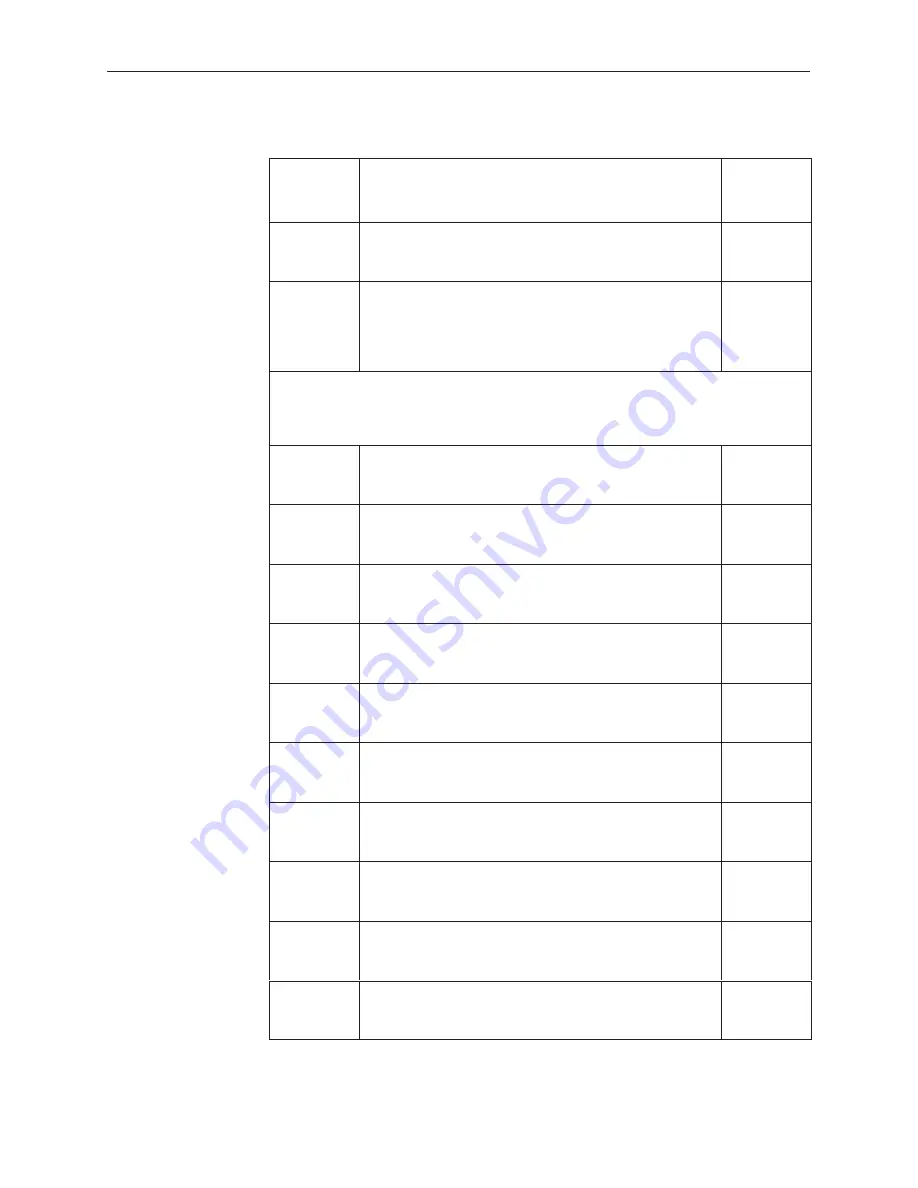

Table 5-8.

Signaling and Trunk Conditioning Values (1 of 2)

Network

Side Value

Meaning

DSX-1 Side

Default

Value

None

No signaling used on this DS0. Use this setting if there is

no voice signaling information being passed on this DS0

(clear channel).

None

RBS

(default)

Robbed Bit Signaling is used on this DS0, but no trunk

conditioning. Signaling bits will be passed to the T1

interface to which this DS0 is cross-connected when this

T1 interface is not in CGA, but the signaling bits will be all

ones when CGA is present.

RBS

The following values will configure the cross-connect for RBS, as well as perform the

trunk conditioning indicated when a CGA condition occurs. Although the ABCD signaling

bits for each setting are described, only AB bits are transmitted when the

cross-connected T1 interface is using D4 framing.

E&M-idle

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the idle state for an E&M

interface (ABCD = 0000).

E&M idle

E&M-busy

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the busy state for an

E&M interface (ABCD = 1111).

E&M busy

FXOg-idle

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the idle state for an FXO

Ground-Start interface (ABCD = 1111).

FXSg-idle

FXOg-busy

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the busy state for an

FXO Ground-Start interface (ABCD = 0101).

FXSg-busy

FXOl-idle

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the idle state for an FXO

Loop-Start interface (ABCD = 0101).

FXSl-idle

FXOl-busy

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the busy state for an

FXO Loop-Start interface (ABCD = 0101).

FXSl-busy

FXSg-idle

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the idle state for an FXS

Ground-Start interface (ABCD = 0101).

FXOg-idle

FXSg-busy

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the busy state for an

FXS Ground-Start interface (ABCD = 1111).

FXOg-busy

FXSl-idle

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the idle state for an FXS

Loop-Start interface (ABCD = 0101).

FXOl-idle

FXSl-busy

The signaling bits transmitted to the cross-connected T1

interface during a CGA represent the busy state for an

FXS Loop-Start interface (ABCD = 1111).

FXOl-busy

Summary of Contents for 9161 Single T1

Page 1: ...MODEL 916x 926x T1 ACCESS MUX TECHNICAL REFERENCE Document No 9161 A2 GH30 40 April 1999...

Page 34: ...Management and Control 2 6 9161 A2 GH30 40 April 1999 This page intentionally left blank...

Page 54: ...User Interface 4 10 9161 A2 GH30 40 April 1999 This page intentionally left blank...

Page 92: ...Setting Up 5 38 9161 A2 GH30 40 April 1999 Example Channel Allocation...

Page 142: ...Security 6 10 9161 A2 GH30 40 April 1999 This page intentionally left blank...

Page 252: ...IP Addressing B 8 9161 A2 GH30 40 April 1999 This page intentionally left blank...