ML51/ML54/ML56

Sep. 01, 2020

Page

547

of 719

Rev 2.00

ML

51

/ML

54

/ML

5

6 S

E

RI

E

S

TECHNI

CA

L

RE

F

E

R

E

NC

E

M

A

NU

A

L

ML51/M

L54

/M

L56

Series

Tec

hnical Reference

Manual

occurred during a transaction. A bus error is caused by a START or STOP condition appearing

temporally at an illegal position such as the second through eighth bits of an address or a data byte,

and the acknowledge bit. When a bus error occurs, the SI flag is set immediately. When a bus error is

detected on the I

2

C bus, the operating device immediately switches to the not addressed salve mode,

releases SDA and SCL lines, sets the SI flag, and loads I2CnSTAT as 00H. To recover from a bus

error, the STO bit should be set and then SI should be cleared. After that, STO is cleared by hardware

and release the I

2

C bus without issuing a real STOP condition waveform on I

2

C bus.

There is a special case if a START or a repeated START condition is not successfully generated for

I

2

C bus is obstructed by a low level on SDA line e.g. a slave device out of bit synchronization, the

problem can be solved by transmitting additional clock pulses on the SCL line. The I

2

C hardware

transmits additional clock pulses when the STA bit is set, but no START condition can be generated

because the SDA line is pulled low. When the SDA line is eventually released, a normal START

condition is transmitted, state 08H is entered, and the serial transaction continues. If a repeated

START condition is transmitted while SDA is obstructed low, the I

2

C hardware also performs the same

action as above. In this case, state 08H is entered instead of 10H after a successful START condition

is transmitted. Note that the software is not involved in solving these bus problems.

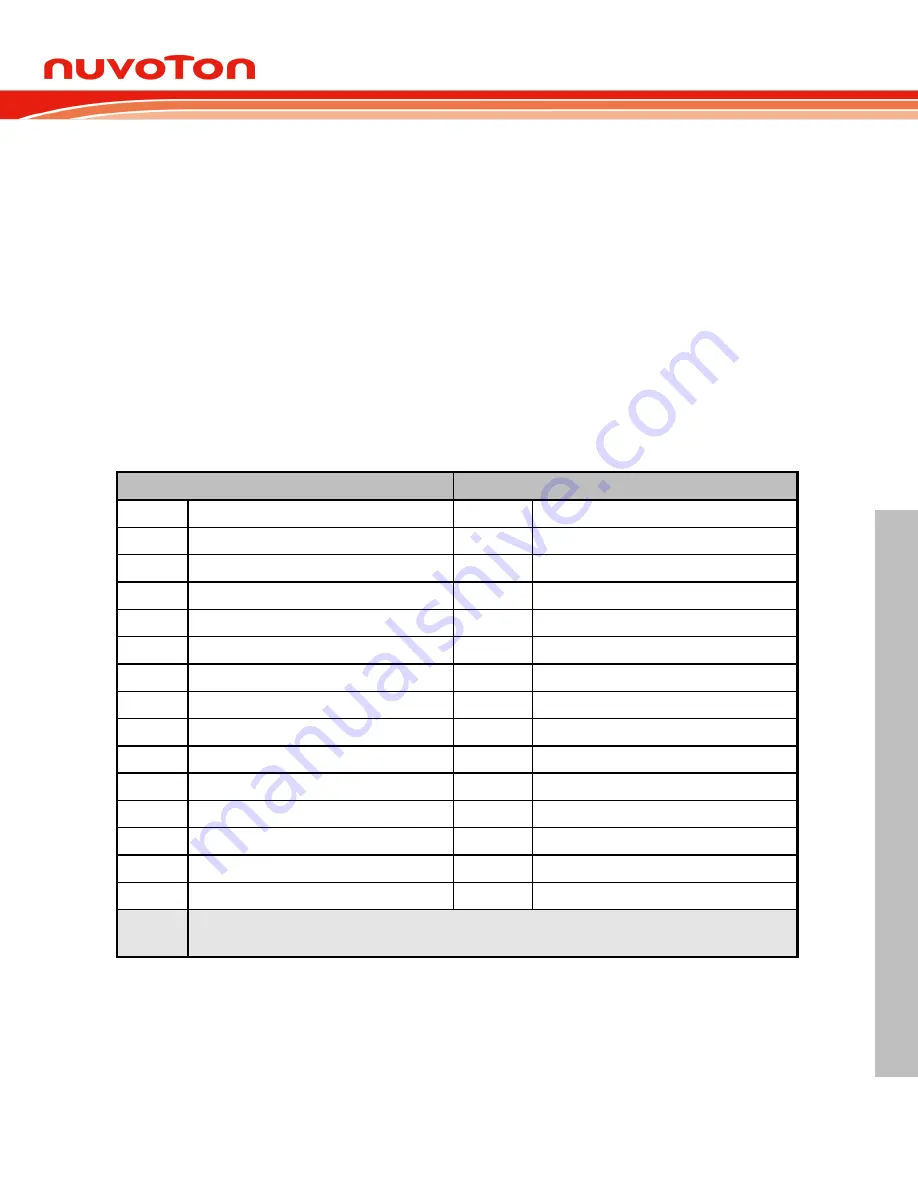

The following table is show the status display in I2STAT register of I

2

C number and description:

Master Mode

Slave Mode

STATUS

Description

STATUS

Description

0x08

Start

0xA0

Slave Transmit Repeat Start or Stop

0x10

Master Repeat Start

0xA8

Slave Transmit Address ACK

0x18

Master Transmit Address Ack

0xB0

Slave Transmit Arbitration Lost

0x20

Master Transmit Address Nack

0xB8

Slave Transmit Data ACK

0x28

Master Transmit Data Ack

0xC0

Slave Transmit Data NACK

0x30

Master Transmit Data Nack

0xC8

Slave Transmit Last Data ACK

0x38

Master Arbitration Lost

0x60

Slave Receive Address ACK

0x40

Master Receive Address Ack

0x68

Slave Receive Arbitration Lost

0x48

Master Receive Address Nack

0x80

Slave Receive Data ACK

0x50

Master Receive Data Ack

0x88

Slave Receive Data NACK

0x58

Master Receive Data Nack

0x70

GC mode Address ACK

0x00

Bus Error

0x78

GC mode Arbitration Lost

0x90

GC mode Data ACK

0x98

GC mode Data NACK

0xF8

Bus Released

Note:

Status “0xF8” exists in both master/slave modes, and it won’t raise interrupt.

Figure 6.12-14 Status Display In I2STAT Register

6.12.4 I

2

C Time-Out

There is a 14-bit time-out counter, which can be used to deal with the I

2

C bus hang-up. If the time-out

counter is enabled, the counter starts up counting until it overflows. Meanwhile I2TOF will be set by

hardware and requests I

2

C interrupt. When time-out counter is enabled, setting flag SI to high will

reset counter and restart counting up after SI is cleared. If the I

2

C bus hangs up, it causes the SI flag