ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

768

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

register is a shadow register of highest priority EADC_DAT register. The lower number sample

module is higher priority. After PDMA read EADC_CURDAT register, the VAILD of the shadow

EADC_DAT register will be automatically cleared.

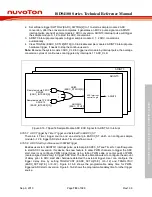

6.16.5.14 Interrupt Sources

The ADC converter generates ADIFn (EADC_STATUS2[3:0], n=0~3) at the start of conversion or

the end of conversion decide by INTPOS (EADC_SCTLn[22], n=0~12). If ADCIENn

(EADC_CTL[5:2], n=0~3) is set then conversion end interrupt request ADINTn (n=0~3) is

generated. The controller of interrupts is shown as Figure 6.16-14

ADIF0 (EADC_STATUS2[0])

ADCIEN0 (EADC_CTL[2])

ADINT0

ADIF1 (EADC_STATUS2[1])

ADCIEN1 (EADC_CTL[3])

ADINT1

ADIF2 (EADC_STATUS2[2])

ADCIEN2 (EADC_CTL[4])

ADINT2

ADIF3 (EADC_STATUS2[3])

ADCIEN3 (EADC_CTL[5])

ADINT3

ADCMPF0 (EADC_STATUS2[4])

ADCMPIE0 (EADC_CMP0[1])

ADCMPF1 (EADC_STATUS2[5])

ADCMPIE1 (EADC_CMP1[1])

ADCMPF2 (EADC_STATUS2[6])

ADCMPIE2 (EADC_CMP2[1])

ADCMPF3 (EADC_STATUS2[7])

ADCMPIE3 (EADC_CMP3[1])

Figure 6.16-14 ADC Controller Interrupts

6.16.5.15 ADC

Power Management and Calibration

There are three kind of power saving modes, including ADC Deep Power-down, ADC Power-down

mode and ADC Standby mode. User can configure PWDMOD (EADC_PWRM[3:2]) to select which

power saving mode EADC would enter when ADCEN (EADC_CTL[0]) is set as 0.

The difference of these power down mode is shown as Table 6.16.5-2. Because the internal LDO

will be shut down in Deep Power-down and Power-down mode, EADC needs to take extra time to

resume. The interval of time to resume is set by LDOSUT (EADC_PWRM[19:8]) which must be

longer than 20 us. As for the Standby mode, LDO will keep enable and start-up time is unnecessary.

Power Supplies

Deep Power-Down

Power-Down

Standby

Internal LDO

Disable

Disable

Enable

Internal power switch

Disable

Enable

Enable