2-4

|

ni.com

Chapter 2

Analog Input

When one or more sigma-delta modules are in an analog input task, the sigma-delta modules also

provide the signal used as the AI Sample Clock. This signal is used to cause A/D conversion for other

modules in the system, just as the AI Sample Clock does when a sigma-delta module is not being used.

When sigma-delta modules are in an AI task, the chassis automatically issues a synchronization

pulse to each sigma-delta modules that resets their ADCs at the same time. Because of the

filtering used in sigma-delta A/D converters, these modules usually exhibit a fixed input delay

relative to non-sigma-delta modules in the system. This input delay is specified in the C Series

module documentation.

Slow Sample Rate Modules

(cDAQ-9184/9188)

Some C Series analog input modules are specifically designed for

measuring signals that vary slowly, such as temperature. Because of their slow rate, it is not

appropriate for these modules to constrain the AI Sample Clock to operate at or slower than their

maximum rate. When using such a module in the cDAQ chassis, the maximum Sample Clock

rate can run faster than the maximum rate for the module. When operating at a rate faster than

these slow rate modules can support, the slow rate module returns the same point repeatedly,

until a new conversion completes. In a hardware-timed task, the first point is acquired when the

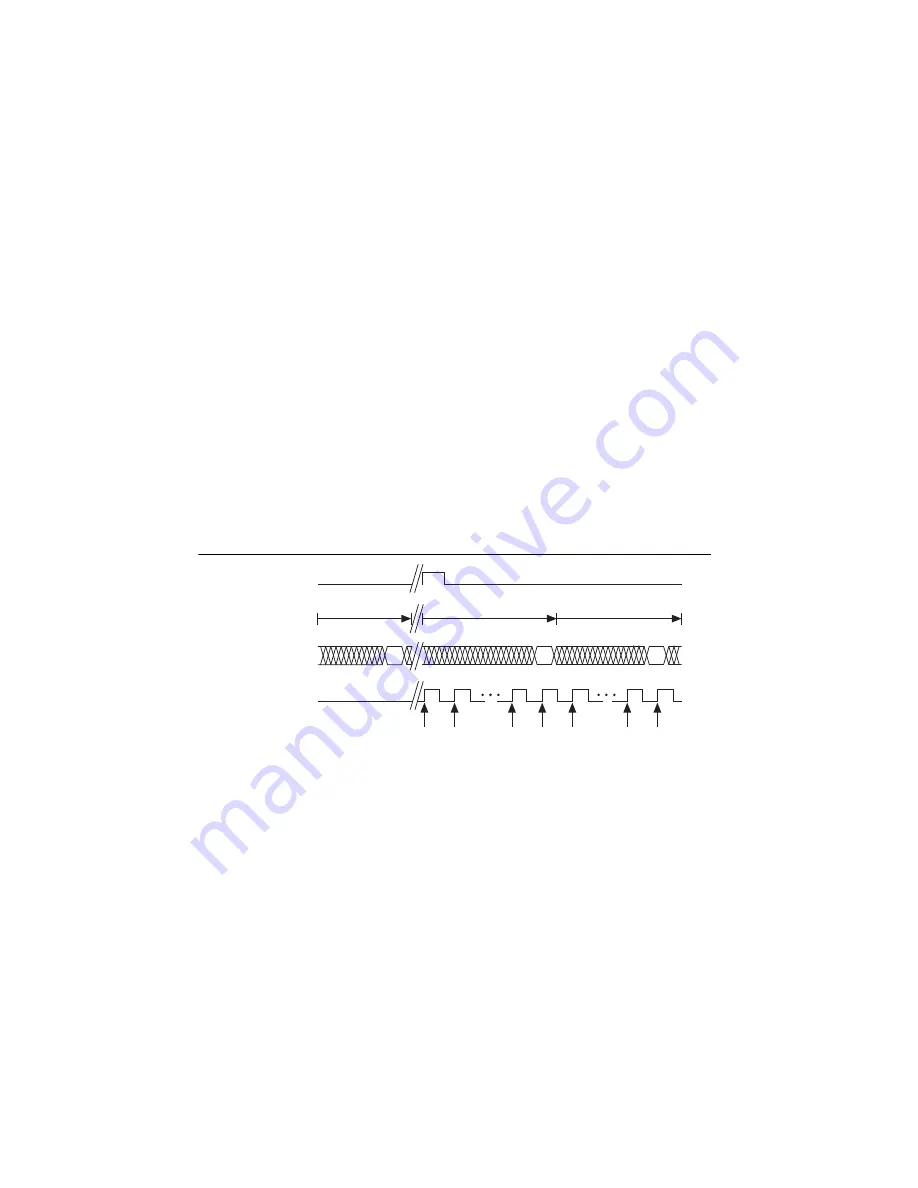

task is committed. The second point is acquired after the start trigger as shown in Figure 2-2.

Figure 2-2.

Sample Clock Timing Example

For example, if running an AI task at 1 kHz using a module with a maximum rate of 10 Hz, the

slow module returns 100 samples of the first point, followed by 100 samples of the second point,

etc. Other modules in the task will return 1,000 new data points per second, which is normal.

When performing a single-point acquisition, no points are repeated. To avoid this behavior, use

multiple AI timing engines, and assign slow sample rate modules to a task with a rate at or slower

than their maximum rate.

Refer to

C Series Support in NI-DAQmx

for more information. To access this document, go to

and enter the Info Code

rdcdaq

.

S

t

a

rtTrigger

D

a

t

a

from

A/D Conver

s

ion

(

S

low Mod

u

le)

Sa

mpleClock

D

a

t

a

Ret

u

rned

to AI T

as

k

1

s

t A/D Conver

s

ion

2nd A/D Conver

s

ion

3

rd A/D Conver

s

ion

A

B

C

A

A

A

B

B

B

C